| |

Строительный блокнот Корпуса микропроцессорных микросхем

41 с ♦ 5 6 7 At!/ AKMI i>AKSl SYmt srmi KZ 0 - s 6 AKM2I. AKSZi SYf/fKZ SYHZKZ 10 11 JL Jl. JL JL 16 АКМЗ aks3 22 19 Z1 i-Z Рис. 7.9. Условное графическое обозначение КР587ИКЗ идентификаторами приема н выдачи информации Регистр микрокоманд (РМК) предназначен для приема и хранения кода поступающей в AEU микрокоманды, разрядность -7. Дешифратор микрокоманд (ДШ) служит для формирования управляющих сигналов Входы дешифратора подключены к регистру микрокоманд. Кроме того, дешифратор Стробируется сигналами з блока синхронизации. Регистр РА предназначен для приема и хранения исходного операнда, поступающего по каналу К1, разрядность - 8. Регистр РВ предназначен для приема и хранения исходного операнда, поступающего по каналу К2, разрядность -8. Регистр РП1 предназначен для хранения младшей части произведения при операциях умножения и результата операции при сдв1игах влево, разрядность - 8 2J22 , nsj J6 Схема обме -I на. \ C02 Ьлон умношения Блои суммирования блок поиска содов

BiPC ЛШ i9i.ni.- Рис. 7.10. Структурная схема КР587ИКЗ

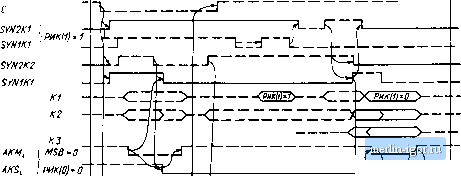

Схема обмена cat АНН, AHS! Схема обмена СОЛ AK.4J 5УШ2 IMSB=0 SYNiKII MSB=0 \РИК10,1)  q Рнс. 7.11. Временная диаграмма работы КР587ИКЗ Мнемокод Код операции Описание операции САП САЛ СЦП УК К1 K2-*Kt, К2 УК К1, К2-*К2 УК К1-К2 УА К1, К2-К2 УА К1, К2-*К2 УА Kl--Kl К2 УА k:1-K2 3 PAKl 3 PBKJ В pni-/c/ В РП2-К2 ПКНБ ЗРИК 00 I ООО о 1 I 0 I о 1 о 1 ВС ВС ВС ВС ВС 1 о о о о о ВС 1000 01 ВС I ООО 1 I ВС 100100 ВС 1001 о 1 ВС 100 1 1 о ВС 1 о о 1 1 1 ВС 1 1 100 о ВС 1 1 1001 ВС 1 I 1 о 1 о ВС I 1 1 о 1 1 ВС II I 100 ВС 1 1 1 1 о 1 ВС 1 1 1 1 1 о ВС I 1 OjV А-О 1 1 1 1 1 1 А- Сдвиг лог вправо Сдвнг лог влево Сдвнг арнфм вправо Сдвиг арифм влево Сдвиг цикл вправо Умножение кодовое KIAK2 с выдачей младшей части результата в KI, старшей части в К2 Умножение кодовое К1/\К2 с выдачей старшей части результата в К2 Умножение кодовое К1/\РВ с выдачей старшей части результата в К2 Умножение арифм К1-К2 с выдачей младшей части результата в К1, старшей части в К2 Умножение арифм К1 К2 с выдачей старшей ча стн результата в К2 Умножение арифм А/-РВ с выдачей младшей части результата в К1, старшей части в К2 Умножение арифм KI РВ с выдачей старшей ча сти результата в К2 Загрузка РА из KI Загрузка РВ из К2 Выдача РП1 в К1 Выдача РП2 в К2 Поиск кода левою нуля Поиск кода левой единицы Поиск кодов левой пары неравнозначных бит Загрузка РИК из РМК Начальная установка Примечания I В описаниях микрокоманд символ iV в микрокомандах сдвига определяет число р.прядов на которое производится сдвнг, а в микрокомандах загрузки РИК определяет код загружаемый н этот регистр 2 x состояние разряда микрокоманды безразлично Регистр РП2 предназначен для хранения старшей части произведения при операциях умножения, результата операции при сдвигах вправо и кода бита прн операции поиска битов разрядность - 8 Регистр именного кода (РИК) предназначен для организации объединения однотипных микросхем AEU в блок с общим микропрог раммным упавленнем (рис 7 12) В зависимости от расположения микросхем в соответствующем вертикальном ряде в РИК заносится следующий код 01-крайний левый рят 10 - крайний правый ряд, И-остальные ря ды, 00 - если имеется только один вертикаль ный ряд, разрядность - 2 Триггер установки (ТУ) отмечает прн объ единении в блок AEU верхний ряд микросхем Это достигается установкой ТУ в нулевое состояние с помощью подключения вывода SYN2K2 к общей шине Блок умножения предназначен для выпол нення операций умножения над операндами в РА и РВ с получением младшей и старшей частей произведения и операций сдвига над операндами в РА Операнды могут представлять собой либо целые числа без знака, либо целые числа со знаком в старшем разряде в дополнительном коде Блок умножения состоит нз матрицы одноразрядных сумматоров, с помощью которых происходит получение и сдвиг частичных сумм Блок суммирования предназначен для суммирования частичных произведений при матричном объединении однотипных микросхем AEU в блок с общим микропрограммным управлением Входы блока суммирования соединены с выходами блока умножения Результат суммирования заносится в РП2 Кроме того, в блок суммирования поступает через вывод Р сигнал переноса Перенос из блока сумми рования через БФС поступает в К3(2) Блок поиска кодов битов предназначен для выполнения операции поиска ко la левого -нулевого бита, левого единичного бита, левой пары неразвнозначныч битов над операн шм в РВ

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||