| |

Строительный блокнот Корпуса микропроцессорных микросхем

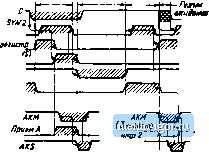

функциональное назначение выводов Информация канала к2, 2-й разряд Информация канала к1, 2-й разряд Информация канала к2, 3-й разряд Информация канала К/, 3-й разряд Сигнал установки в исходное состояние Сигнал, свидетельствующий об окончании приема по каналу к1 Сигнал, сопровождающий выдаваемую информацию по каналу к1 Сигнал, свидетельствующий об окончании приема по каналу к2 Сигнал, сопровождающий выдаваемую информацию по каналу к2 Сигнал, сопровождающий выдаваемую информацию по каналу КЗ Сигнал, свидетельствующий об окончании приема по каналу КЗ Синхронизация ALU Сигнал, свидетельствующий об окончании операции Сигнал разрешения приема и выполнения микрокоманды Сигнал, кодирующий признак старшего модуля в группе совместно работающих микросхем ALU Информация регистра микрокоманд, 11-й разряд Сигнал разрешения обмена работы по первому информационному каналу Сигнал, кодирующий состоянне цепи переноса старшего разряда Сигнал, кодирующий состояние цепи переноса из старшего разряда Информация канала КЗ, 3-й разряд Общий Информация канала КЗ, 2-й разряд Информация канала КЗ, 1-й и 0-й разряды Сигнал, кодирующий состояние цепи переноса младшего разряда Сигнал, кодирующий состоянне цепи переноса в младший разряд Информация регистра микрокоманд Информация канала к1, 0-й разряд Информация канала к2, 0-й разряд Информация канала к1, 1-й разряд Информация канала к2, 1-й разряд Напряженке питания * с тремя состояниями. Активный - низкий уровень. Активный - высокий уровень. С асинхронным переносом и входных мультиплексоров по шинам А и Б. АЛУ выполняет арифметические операции (сложение с I, сложение, вычитание) н логические (конъюнкция, дизъюнкция, сложение по модулю 2, инверсия). Входные мультиплексоры коммутируют поступающие операнды иа входы АЛУ. В АЛУ формируются также два сигнала, индицирующие состояние АЛУ при выполнении операций; переполнения (ПП) и расигирення 23 22 20 Ю ri 27 у 28°- :hs2 IMS* J/<> SO<i SSo- IHSIO Схема о5ме~ на CO] T.o\rnn\TSH\r,/ Блок сдВигателя Щв) memmo-/. мческий Вмк (АЛУ) Шина Б Блок регистров оБщего иаоначения (РОН) Ра В регистр А Схема обмени COI JS 40 2 4 J3 il 1 J Схема OS-меиа C02 olB orS smj2 -oil. 021 Рис. 7.2. Структурная схема КР587ИК2 (TP). Сигналом ПП является неэквивалентность между переносами из третьего и четвертого разрядов. Сигнал TP - это перенос из старшего разряда РЗ. Блок регистров общего назначения предназначен для хранения данных внутри микро- ом л * foia чтение Фат записи Запись! микрмемакВШ ПриьмА  Запись Рнс. 7.3. Временные диаграммы работы КР587ИК2 схемы ALU. Блок включает восемь 4-разрядных регистров (РОН), доступных микропрограммно. Содержимое оегнстров поступает на входы АЛУ по шинам считывания А н £ Запись информащнн в одни из регистров осуществляется с шины записи Д Блок сдвнгателя предназначен для выполнения операций логического и циклического сдвигов на один разряд вправо н влево. В блоке сдвнгателя формируются также трн сигнала состояний ALU: знак (ЗН - старший разряд результата), сравнение с О (СРО) и расширение (TP - выпадающий при сдвигах разряд). Рабочий регистр А предназначен для записи и хранения 4-разрядных кодов результата, полученных при выполнении микрокоманды При операциях обмена А выполняет функцию буферного регистра внешних каналов К1-КЗ. Регистр состояния (PC) предназначен для нднкацнн состояний АЛУ. Регистр включает триггер сравнения с нулем Т 0 , триггер переполнения ТПП, триггер знака ТЗН, триггер расширения TP Сигналы состояния заносят- ся в PC и выдаются в КЗ, если в микрокоманде есть признак выдачи состояний (ВС) - наличие лог. 1 в последнем разряде микрокоманды (МК11) причем при операциях сдвига в триггер расширения заносится сигнал TP, при остальных операциях TP Регистр состояния при выполнении отдельных операций с константой функционирует как регистр общего назначения. Регисто микрокоманды (РМК) предназначен для записи и хранения кода микрокоманды, поступающей в АЛУ. Дешифратор микрокоманд (ДШ) служит для формирования управляющих сигналов. Входы дешифратора подключены к регистру микрокоманд Дешифратор стробируется сигналами из блока синхронизации. Каналы К1-КЗ предназначены для приема и выдачи информации. Каналы К1 и К2 принимают и выдают информацию из рабочего регистра Л. Канал КЗ пшнннмает информацию в рабочий регистр Л. а выдает из PC. Схемы обмена СО!-СОЗ управляют приемом нли выдачей информации в (из) ALU, вырабатывают сопровождающие выдаваемую информацию сигналы AKMI, отмечают прием информации сигналами AKSI Прн работе нескольких источников информации на один канал наличие сигнала AKSI свидетельствует о занятости канала и блокирует выдачу информации из ALU. При незавершившемся обмене по KI и К2 в Предыдущей микрокоманде схемы обмена COl или С02 блокируют выполнение следующей микрокоманды до окончания обмена. Если выдача информации в КЗ не завершена, то схема обмена СОЗ не блокирует выполнение следующей микрокоманды при отсутствии в ней признака ВС Блок расширения предназначен для дискретного (по четыре бита) наращивания разрядности АЛУ без включения дополнительного оборудования объединением выводов Р/-РЗ, Р2-Р4 и соответствующей установкой потенциала на выводе MSB. В старшем полубайте MSB подключен к общей шине, в остальных - к шине питания. По связям Р1-РЗ, Р2-Р4 передаются сигналы сдвигаемых разрядов и сигналы переносов Блок синхронизации предназначен для организации цикла выполиення микрокоманды. Цикл выполнения начинается при поступлении сигнала С либо положительного фронта сигнала на выводе SYN2 и проходит последовательно три фазы, прием, чтение, запись. Временная диаграмма работы приведена на рис. 7.3 Выводы SYN2 и SYNI индицируют все три состояния исполнения микрокоманды Подача на эти выводы управляющих сигналов извне позволяет задерживать цикл выполнения любой микрокоманды. Микросхема ALU может находиться в режиме выполнения микрокоманды или в режиме ожидания прихода следующей. Цикл выполнения микрокоманды (см рис 7.3) начи- нается с приходом отрицательного фронта сигнала С (прн этом на входах РМК извне должен быть установлен код микрокоманды) и проходит три фазы исполнения: прием, чтение и запись. Прием начинается с момента поступления сигнала С, который вызывает запуск БС и формирование уоовня лог. 1 на выводе SYN2. Сигнал иа выводе SYN2 свидетельствует о начале приема микрокоманды в РМК. Отрицательный фронт сигнала SyN2 (окончание интервала приема) появляется лишь в том случае, если окончена выдача в KI и К2 в предыдущей микрокоманде, окончен прием новой микрокоманды, в микрокоманде есть признак приема информации - окончен прием информации из KL Если хотя бы одно из условий не выполнено, то ALU переходит в режим ожидания и лишь при выполнении всех условий возникает отрицательный фронт сигнала SYN2, который вызывает сигнал AKSJ, свидетельствующий об окончании приема информации по KI Сброс сигнала AKMI влечет за собой сброс сигнала AKSL Информация, принятая по /С/, записывается в рабочий регистр А С появлением отрицательного фронта SYN2 начинается фаза чтения н возникает отрицательный фронт сигнала SYNL Информация, считанная из двух источников, по шннам А н Б поступает на входы АЛУ, где происходит выполнение операции и запись результата в регистр промежуточного хранения результата. Об окончании фазы чтения и о начале фазы записи свидетельствует положительный фронт сигнала SYN1, который вызывает формирование положительного фронта сигнала SYN2. Во время записи выполняются операции сдвига в сдвигателе и запись результата в приемники информации: РОН, А, PC в зависимо-стн от кода микрокоманды. Об окончании записи свидетельствует отрицательный фронт сигнала SYN2. С этого момента начинается выдача информации в KL Окончание записи переводит ALU в исходное состояние для приема новой микрокоманды. Поэтому фазы выдачи информации и приема следующей микрокоманды могут совмещаться, однако окончание приема в следующей микрокоманде не наступит до момента освобождения канала. Выдача результата операции в Ю происходит в том случае, если к моменту выдачи сигнал AKSJ отсутствует [AKSI должен быть в со-стояннн лог. 1). Сигнал AKMI сопровождает выданную в Л/ информацию, а сброс информации осуществляется при поступлении извне сигнала AKSI, который формирует положительный фронт сигнала AKML Следует отметить, что прием и выдачу информации можно осуществлять в формате микрокоманд с обменом и в случае приема из КЗ-в формате с константой. В зависимости от кода в разрядах О и 1 РМК 12-разрядная микрокоманда ALU разбивается на поля, образуя четыре формата мик-рокома1нд (табл. 7.3). Во всех форматах микрокоманд разряды

|