| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Состояние разрядов микрокоманды. Поле Т Состояние разрядов РУБ Выбираемые разряды D0 - DI5 Таблица 6.16

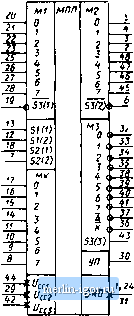

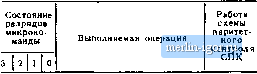

6.4. Микросхема К584ВВ1 Микросхема К5в4ВВ1 - магистральный приемопередатчик, предназначена для приема, хранения и передачи байтов информации между тремя двунаправленными магистралями. Две магистрали предназначены для внутри-процессорного обмена, а третья, имеющая по-выщеиную нагрузочную способность, - для организации интерфейса микро-ЭВМ. Условное графическое обозиачеиие микросхемы приведено на рис. 6.16, назначение выводов - в табл. 6jI9, структурная схема дана на рнс. 6.17, система микрокоманд - в табл. 6.20, 6.21, формат микрокоманд показан на рис. 6.18. Таблица 6.17

Таблица 6.18

Рис. 6.16. Условное графическое обозначение К584ВВ1 Вывод Обозначение Тип вывода Функциональное назначение выводов W-23, 25-28 5-2, 48-45 13, 12 18, 7 19, 6, 43 17-14, 11-8 32-35, 38-41 37, 36 30 44, 29, 42 1. 24, 31 Ml (0)-М1 (7) М2 (0)-М2 (7) 51 (1), S1 (2) 52 (1), S2 (2) S3 (I), S3 (2), S3 (3) МК (0)-МК (7) МЗ {3)-М3 (7) А. К УП Ucci, Uccj, Uccz GND Входы/ выходы Входы/ выходы Входы Входы Входы Входы Входы/ выходы Входы/ выходы Вход Двунаправленная магистраль внутрипроцессорного обмена Двунаправленная магистраль внутрипроцессорного обмена Синхросигналы занесения микрокоманды Синхросигналы занесения данных в РР1, РР2 соответственно Синхросигналы выдачи данных на магистрали Ml-МЗ Шина микрокоманд Двунаправленная умощнен-ная магистраль Выводы схемы паритетного контроля магистрали МЗ Управление током потребления микросхемы и нагрузочной способностью магистрали МЗ Напряжения питания Общий  Hll2=t> Регистр Схема ттрв-м портних замытти ЪТматри\ЖЛ

вщ/трепта > сиемли

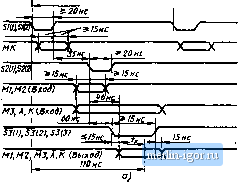

Рнс. 6.17. Структурная схема K584BBI Задание функции, исполняемых микросхемой в каждом такте, производится подачей в шнну микрокоманд Вразрядного кода. Младшая половина шины микрокоманд (МКО- МКЗ) предназначена для управления передачами по магистрали Ml и приема в регистр данных PPI, старшая часть (МК4-МК7) - для управления передачами по магистрали М2 н приема в регистр данных РР2. При приеме данных в микросхеме из мапи-стралн МЗ в схеме паритетного контроля осуществляется передача контрольных разрядов, образуемых как сумма по модулю два передаваемой информации и входного сигнала, от входа А к выходу Л. при выдаче - в обратном направлении от /С к Л. Если же магистраль МЗ работает одновпеменно на вход и на выход, то формирование контрольных результатов разрядов осуществляется, как прн выдаче, т. е. от /С к А. Микросхема синхронизируется тремя группами синхроеернй: 5/, 52 и S3. Первая серия Sl(l), Si(2) стробирует занесение кодов с /Тале управления передачами по магистрали Mt I I I -1 I-1- /1але дпраВлемия передачами по магистрали М2 Рис. 6.18 Формат микрокоманд микросхемы К584ВВ1 Таблица 6.20 Гс 120 НС  Отсутствие действия Передача информации из регистра данных РР2 на магистраль Ml Передача информации из магистрали Ml через регистр данных РР1 в магистраль МЗ Передача информации из магистрали МЗ через регистр данных РР2 в магистраль Ml Передача информации из магистрали Ml в регистр данных РР1 Передача информации из регистра данных РР1 в магистраль Ml Передача информации из регистра данных РР1 в магистраль МЗ Передача информации из магистрали МЗ в регистр данных РР1 Отсутствие действия Передача информации из магистрали М2 в магистраль Ml Передача информации из магистрали Ml в магистраль МЗ Передача информации из магистрали МЗ в магистраль Ml Отсутствие действия Передача информации из магистрали МЗ в магистраль Ml Передача информации из магистрали Ml в магистраль МЗ Отсутствие действия Отсутствие действия То же Отсутствие действия То же А->К Отсутствие действия То же К->-А АК Примечание. Схема паритетного контроля СПК осуществляет передачу К-►Л, если имеется выдача в магистраль МЗ во втором канале. Рис. 6.19. Временные диаграммы работы К584ВВ1 в различных режимах: а - с использованием внутренних регистров и схем контроля; б -с использованием внутренних регистров; в -с использованием схем контроля; г - без использования внутренних регистров и схем контроля  Гс 100 нс 20 НС 15 НС 9 20 нс Ml,M2,f13(Bbixodj SO НС ЧГ5МС 5201,5212) Гс * 100 НС *гвнс

920нс 5т]Ш)\ 9 а не 520XSX.) мТЩмз (Вход) 53(0,5312. 53(3) М1,М2.МЗ (Выход) Гс 70нс ?)5нс 35нс *(5ис XZX XZX- \- 15нс fC </5мс/ SOhc f

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||