| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Основные параметры К583ВА1 Напряжеине питания Ucc 5 В±10% Ток потребления /сс, не более 100 мА Входной ток низкого уровня liL, не более: для входов S5-S7 .... -0,5 мА для входов S7-S4, L1. U . -0,25 мА для входов Z.3, А, К . -0,2 мА Входной ток высокого уровня liH, не более....... 50 мкА Выходное напряжение высокого уровня UoH по магистрали L3, ие менее....... 2,4 В Выходной ток низкого уровня loL, ие более: по магистралям LI, L2 . . 20 мА по магистрали L3..... 53 мА Время задержки передачи информации tp, не более ... ПО не 5.8. Микросхема К583ВА2 Микросхема К583ВА2 - магистральный приемопередатчик (МПП) без памяти, выполненный на основе маломощной ТТЛШ-техно-логин, предназначен для согласования и обмена информацией между двумя типовыми однонаправленными магистралями и мощной двунаправленной магистралью. Условное графическое обозначение микросхемы прнведе-10 на рис. 5.32, назначение выводов - в табл. 5.22, структурная схема дана на рнс. 5.33, таблица истинности i-ro разряда для сигналов положительной логики - в табл. 5.23, временная диаграмма работы - на рис. 5.34, электрические схемы входных и выходных согласующих каскадов показаны на рнс. 5.35. Микросхема обеспечивает межмагистраль-ный обмен данными между мощной магистралью и двумя типовыми однонаправленными магистралями в четырех направлениях. Структурная схема МПП, приведенная на рис. 5.33, содержит следующие функциональные узлы: пять входных одноразрядных информационных магистралей L1(0)-Ll(4); пять выходных одноразрядных магистралей с открытым коллектором L2(0)-L2(4); пять двунаправленных одноразрядиых информационных магистралей L3(0)-L3(4) с открытым эмиттером; пять входов синхронизации S1(0)-SI(4) для стробирования передачи информации по соответствующим разрядам от L1 к /Запять входов синхронизации для стробирования передачи информации по соответствующим от L3 к L2: пять блоков усилителей формирователей. Информация 00 входов L1(0)-L1(4) передается на выходы L3(0)-L3(4) прн наличии разрешающих сигналов Sl(0)-Sl(4) (лог. 0); при этом информация на выходах L3 инвертирована по отношению к магистрали LI. Информация с входов/выходов 13(0)- L3(4) передается на выходы L2(0)-L2(4) при наличии разрешающих сигналов на соответствующих входах S2(0)-S2(4); при этом информация на выходах L2 инвертирована по отношению к информации на входах/выходах L3. Информация с входов LI(0)-L1(4) может быть передана на выходы L2(0)-L2(4) при наличии разрешающих сигналов на соответствующих входах обеих синхроеернй S1, S2, при этом информация иа выходах L2 прямая по отношению ко входам L1. ±

Таблица 5.22 Рнс. 5,32, Условное графическое обозначенне К583ВА2

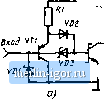

srlo)- sidi Lilfl L2(ll S2l.ll Sf(2) imi - 12(21 S2(2>. U(3! - 1.2(31- S2(3I -Sl(4 uCfl - 13(3) L3[kl Рис. 5.33. Структурная схема K583BA2 Г- s Вход SI *Smc а г/Уда J2 625no Выход LZ ~ t,20HC S/fc <,25hc. 42SHC *Snc. U2SMC Рнс. 5.34. Временная диаграмма работы К538ВА2  \ 7nt вхад/вшод s/ Vi7Z J VB3 3 jvav Рис. 5.35. Электрические схемы входных (а), выходных (б) и двунаправленных (в) согласующих каскадов микросхемы К583ВА2 Таблица 5.23

Основные параметры К583ВЛ2 Напряжение питания Ucc 5 В±10% Ток потре(5ления /сс, не более . . 80 мА Входной ток низкого уровня I,l, не более.......... -0.2 мА Входной ток высокого уровня llH, не более..........50 мкА Выходной ток низкого уровня Iol: для магистрали L2 ..... 20 мА для магистрали L3..... 53 мА Типовое время задержки передачи информации между магистралями tp...........10-25 НС 5.9. Микросхема К583ВАЗ Микросхема К5вЗВАЗ - быстродействующий универсальный коммутатор магистралей (УК), выполненный на основе маломощной 23 2S 29 Ж

f 2 J 4 5 6 Рис. 5.36. Условное графическое обозначение К583ВАЗ

ТТЛШ-технологни, предназначен для построения коммутаторов, мультиплексоров данных, буферных устройств хранения и логической обработки данных, устройств восстаиовления информации в системах с резервироваяием. Условное графическое обозначение микросхемы приведено на рис. 5.36, назначение выводов - в табл. 5.24, структурная схема дана на рис. 5.37, формат микрокоманд показан на рис. 5.36, система микрокоманд приведена в табл. 5.26, временная диаграмма работы - Таблица 5 25 на рнс. 5.39, электрические схемы входных и выходных согласующих каскадов - на рнс. 6.40. Микросхема обеспечивает выполнение следующих операций. межмагнстральиый обмен данными между четырьмя информационными магистралями в 12 направлениях; передачу информации из магистралей в регистры; I я я S К я 5 со о Код микрокоманды Выполняемая операция 1= 1 i = 3 1 = 7 TC-*L1 RG2(L2)L1 RG3 {L3)-*L1 RG4 (L4)-Ll TC-Ll RG1-*L1 Л {RG2, RG3)-*L1 Л {L2, L3)-*L1 V IA{L2, L3), Л (L2, L4), \J(L3. L4)]-*L1 TC-*L2 RGl (L1)-L2 KG3 (L3)*-L2 RG4 (L4)L2 TC-L2 RG2-L2 Л {RG3, RG4)-*L2; Л (L3, L4)-L2 V ULl, L3), ML3, L4), Л (LI, L4)\- -*L2 TC-L3 RGl {L1)-*L3 RG2 {L2)-L3 RG4 (L4)-yL3 TC-L3 RG3-L3 Л (RGl, RG4)L3; Л (LI, L4)-L3 VlMLl. L2), Л {L2, L4), h(Ll L4)]L3 TC-*L4 RGl (L1)->L4 RG2 (L2)-*L4 RG3 (L3)-*L4 TC-*L4 RG4-*L4 Л (RGl, RG2)- Л (LI, L2)-L4 V [Л (LI, L2), Л (L2, L3), Л (LI, L3)]-*L4 Примечания. 1. При (=1 коды приведены для SI. S2; прн j = 5-для S3, S4; при ( = 5 -для S5, S6; при г=7 -для S7, SS. 2. ТС -3-е состояние выхода магистрали 3 V -операция конъюнкции, л-операция дизъюнкции

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||