| |

|

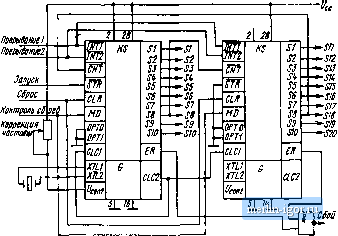

Строительный блокнот Корпуса микропроцессорных микросхем Рис. 5.27. Каскадное включение микросхем К583ВГ1  (более 10) показана на рнс. 5.27. В результате такого соединения суммарное число генерируемых синхросигналов определяется как сумма синхросигналов, генерируемых каждой микросхемой, а общий цикл системы нз нескольких микросхем будет равен сумме циклов работы каждой из микросхем в отдельности Основные параметры К583ВГ1 Напряжение питания Ucci, Vca 5 В±10% Номинальная потребляемая мощность Р: по входу C/cci....... 175 мВт по входу и с а....... 550 мВт Входной ток низкого уровня L, не более: для входов ТШ, CNT, MD, CLR -0,6 мА для входов CLCI, STR, ОРТ . -1,2 мА Входной ток высокого уровня /;н, не более: для входов INT, CNT, МО. CLR для входов CLC1, STR, ОРТ Выходной ток низкого уровня loL, ие более........ Выходной ток высокого уровня /он, не более........ Выходное напряжение низкого уровня UoL, не более..... Выходное напряжение высокого уровня и он, не менее..... Максимальная тактовая частота Рв............ 50 мкА 100 мкА 20 мА 1-1,0 мА 0,5 В 2,4 В 20 МГц 5.7. Микросхема К583ВА1 Микросхема К5вЗВА1 - магистральный приемопередатчик (МОП) с памятью, выполненный на основе маломощной ТТЛШ-технологии, предназначен для согласования и обмена информацией между двумя типовыми магистралями и мощной магистралью; применяется в качестве мультиплексора, коммутатора, буферного регистра, усилителя мощности, контрольного устройства по проверке и формированию контрольных кодов передаваемой информации. Условное графическое обозначение микросхемы приведено на рис. 5.28, назначение выводов - в табл. 5.20, структурная схема показана на рнс. 5.29, алгоритм функционирования - в табл. 5.21, временные диаграммы работы - на рис 5.30, электрические схемы входных и выходных согласующих каскадов - на рис 5.31. Мнкросхема обеспечивает выполнение следующих операций- межмагистральный обмен данными между мощной магистралью и двумя типовыми магистралями в четырех направлениях; передачу информации из магистралей в регистры, передачу информации нз регистров в магистрали; проверку и формирование контрольных кодов передаваемой информации. Структурная схема К683ВА1, приведенная на рис. 5.29, содержит следующие функциональные узлы: две типовые двунаправленные 4-разрядные магистрали данных L1(0)-Ll(3), L2(0)- L2(3) с открытым коллектором; мощную двунаправленную 4-разрядную магистраль данных с открытым эмиттером Z.3; семь входов синхронизации SI-S7 для стробирования передачи информации, 2-разрядную двунаправленную магистраль проверки и формирования контрольных кодов передаваемой информации с открытым эмиттером А, К; два буферных 4-разрядных регистра хранения информации Р1, Р2; схему паритетного контроля, 4-разрядный блок усилителей-формирователей Информация в регистр Р1 (Р2) может быть записана с щин данных Lt(L2) или L3 sT JLisz sS si L2 0 Таблица 5.20 Рис. 5.28. Условное гра фическое обозначение К583ВА1

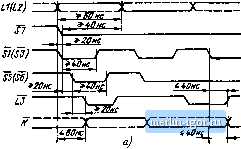

с последующей выдачей в эти же шииы. Передача информации по направлению Ll-*-Pl-*-L3 (L2P2L3) или nPl-Ll (L3P2L2) осуществляется с ниверсией, а Ll->-Pl->-Ll (L2P2-*L2) - без инверсии. Задание режима работы микросхемы осуществляется синхроонгиаламн 5/-S7 в соответствии с алгоритмом, приведенным в табл. 5.211. Синхросигнал S7 определяет направление потока информации нз магистралей L1. L2 в L3 и обратно. При 57=0 реализуется возмож- Регистр буферный (PI) Схема паритетного контроля Feei/cmfi буферный (П) ность передачи данных нз магистралей L1 н L2 в магистраль L3. При 57= 1 разрешена передача данных нз магистрали L3 в любую из магистралей L1 и L2. Синхросигнал 5/  и,/С S7 S2(Sl) >20нс U(LZT А ,2внс f0Hg\ Э. 40нс Рис. 5.30. Временные диаграммы работы К583ВА1 при работе с магистралью L3 (а) и магистралями L1, L2 (б) стробирует заиесеиие информации нз магистрали Z./ в регистр Р1, информация поступает на вход Р1 прн условии 57=0. Синхросигнал 52 разрешает вывод информации нз Р1 на шину L1 при условии 57= 1. Синхросигиал S3 стробирует запись информации нз магистрали L2 в регистр Р2, информация поступает на вход Р2 при условии 57=0. Синхрюоигнал S4 разрешает вывод информации из регистра Р2 на магистраль L2 при 57= 1. Синхросигнал 55 адресует регистр Pt прн записи из магистрали L3 и прн выводе на магистраль L3 Синхросигнал S6 адресует регистр Р2 при записи нз магистрали L3 и при выводе на магистраль L3. Мискросхема содержит встроенную схему паритетного контроля информации магистрали L3; при выводе информации на эту маги- Таблнца 5 21

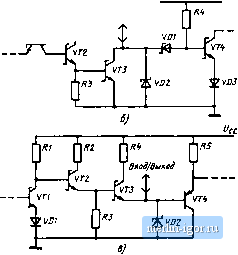

Примечания I В скобках указаны выводы по которым осуществляется паритетный контроль 2 X - состоянне входа безразлично Вкод >- \7VD3  Рис. 5.31. Электрические схемы входных (а), двунаправленных (б) и согласующих (в) каскадов микросхемы К583ВА1 страль паритетной схемой генерируется пятый контрольный разряд (К) до четности или нечетности, а при вводе информации с этой магистрали паритетная схема обеспечивает анализ на четность принимаемой информации, причем вывод К может дополнить контрольный разряд до четности нли нечетности и ре-зультат данных появится на выходе А. Выводы А а К двунаправленные, причем когда они используются как выходы, то представляют собой эмиттерные повторители. Сигналы на выводах А и К формируются по следующим выражениям: А--1(® Гз (0) ф 13(1) ф О (2) Ф Гз (3) J-JeTi (0) ф П(1) ф П(2) ® lT(3), если информация поступает из магистрали Lt, или К -=Хф12(0) ф 12 (I) ф L2(2) ф £7(3), если информация поступает из магистрали L2 Мнкросхема позволяет организовать обмен информацией через линии связи (ЛС) длиной около 65 м, причем разрядность информационных посылок не ограничена.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||