| |

Строительный блокнот Корпуса микропроцессорных микросхем

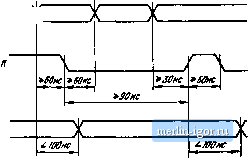

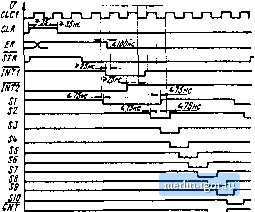

Примечания. 1. Управляющий сигнал R-0. 2. Прн 1=1 коды приведены для SI-S3. прн i-4 -для S4-S6: при i =7 -для S7-S9, при i=iO - для SI0-SI2. 3. Для функционирования микросхемы согласно табл. 5.17 на магистрали, по которым поступает входная информация, должен выдаваться код ООц из логических устройств, соответствующих этой магистрали. 4. Л - операция конъюнкции, V - операция дизъюнкции. Рнс. 5,21. Формат микрокоманд микросхемы К583ХЛ1: S/-S3 - поле управления магистрали LI; S4-Sb - поле управления магистрали L2; S7-S9 - поле управления магистрали L3; S10-312 - поле управления магистрали L4; S/Л - общий сигнал управления ма гистралямн L1 - L4; R сигнал синхронизации регистров PG1 PG4 15/ S2 S3 St S5 S6 S7 sa S9 SfO SK SfZ SI3 R -l J-1-L 2 3 s 6 7 t 3 a II It 13 Вховы Ц SI-SI3 X  Выходы Рис. 5.22. Временная диаграмма К583ХЛ1 работы Основные параметры К583ХЛ1 Напряжение питания Ucc 1,2-5 В Ток питания 1с. ... . 170 мА+> Входной ток высокого уровня н, не более..... 0,2 мА Выходное напряжение низкого уровня UoL. не более 0,4 В Выходной ток высокого уровня /он. не более . . . 0,45 мА Выходной ток низкого уровня loL. не более , . . 20 мА Время задержки передачи информации между магистралями tp. ие более . . . 100 ис 5.6. Микросхема К583ВГ1 Микросхема К5вЗВГ1 предназначена для генерации управляющих синхросигналов, управления пуском и остановом вычислительных устройств, выполнена по ТТЛШ-технологии. Условное графическое обозначение микросхемы приведено иа рис. 5.28, назначение выводов - в табл. 5.18, структурная схема показана иа рис. 5.24, временная диаграмма работы - на рис. 5.26. Микросхема функционально состоит из двух независимых устройств: генератора тактовых импульсов и устройства формирования серии синхросигналов, имеющих отдельные выводы питания. Для работы генератора тактовых импульсов необходимо к выводам XTL1 и XTL2 подключить конденсатор нлн кварцевый резонатор с частотой не боле 20 МГц. Импульсы на выводе CLC2 представляют собой меандр с частотой, определяемой кварцевым резонатором. Вывод t/cont служит для подстройки частоты генератора, если вместо резонатора используется конденсатор. Диапазон изменения напряжения на входе (/cont = 0-5 В. Микросхема требует установки в исходное состоянне, которое осуществляется сигналом CLR высокого уровня. В исходном состоянии на выходах St-SlO и ER присутствует сигнал высокого уровня. Импульс Сброс необходимо подавать только один раз после вклю- чения питания. В дальнейшем переход микросхемы в исходное состояние осуществляется самостоятельно. Для работы микросхемы на вход CLCI должны поступать тактовые импульсы от внешнего генератора илн с выхода генератора CLC2. Устройство формирования серии сннхросиг-налов микросхемы позволяет от одной входной частоты получать 10, 8, 6 или 4 управляющих синхросигнала При этом необходимо произвести коммутацию входов OPTO, OPTli в соответствии с табл. 5.19. Запуск микросхемы осуществляется подачей сигнала STR низкого уровня. Если длительность сигнала STR меньше, чем время цикла работы микросхемы, то геиератия синхросигналов S1-S10 будет осуществляться только один цикл незавйоимо от момежга снятия сигнала запуска STR. Для режима непрерывной генерации необходимо наличие сигнала STR низкого уровня нлн его периодическая подача в каждом цикле. В течение всего времени пе-иерации синхросигналов SJ-StO иа выходе ER будет сигнал низкого уровня, а по окончании геиеращин - сигнал высокого уровня. Мнкросхема генерирует синхросигналы, сдвинутые друг относительно друга на пол-периода входной тактовой серии и имеющие длительность, равную периоду входной так- Таблица 518 Б ывод 3. 4 10 18, 9. 19. 8, 20, 7. 21. 6. 22 13. 12 26. 25 15 17 24 23 2. 28 5. 14 Обозначение XTи. XTL2 иconet CLC2 S1SI0 CLC1 INTI. INT2 CNT OPTI. OPTO STR CLR MB ER Vcc\. Ucci Тип вывода Входы Вход Выход Выходы Вход Входы Вход Входы Вход Вход Вход Выход Функциональное назначение выводов Подключение кварцевого резонатора или конденсатора Подстройка частоты генератора Генератор Синхросигналы Синхронизация Прерывания Продолжение генерации Задание числа генерируемых сигналов Запуск Сброс Задание режима работы Сигнал Ошибка Напряжения питания генератора и микросхемы Общий

JS. z Рис. 5.23. Условное графическое обозначение К583ВГ1 Риистр прерываний t

Регистр запускаг Схема анти-соВпа-дений Регистр запускаЗ

Рис. 5.24. Структурная схема К583ВГ1 товой серии. Прервать генерацию синхросигналов можно подачей сиги а лов низкого уровня на входы IWn, 1NT2, что приведет к закрытию схем совпадения 1, 2 и прекрашенню поступлений тактовой серии синхросигналов 2Shc >2Shc

CLCl И, в свою очередь, прекращению генерации синхросигналов 5/-StO. Возобновление генерации осуществляется повторной подачей сигналов высокого уровня на входы INTI, INT2. Таким образом, наличие входов INTI, INT2 позволяет прервать генерацию синхросигналов S1-SIO с последующим ее возобновлением, причем момент прерывания определяется моментом подачи сигнаг лов прерывания. Микросхема К583ВГ1 имеет встроенную схему определения сбоев, т. е. таких ситуаций, когда по каким-либо поичинам (помехи, сбои по питанию н т. п.) генерируются управляющие сигналы не в соответствии с заданным алгоритмом. При сбое автоматически осуществляется сброс микросхемы в исходное состояние, а на выходе ER формируется сигнал высокого уровня. Для запуска микросхемы после пре-кращения генерации от сбоев необходимо на вход CNT подать сигнал низкого уровня. Схема определения сбоев может быть отключена подачей на вход MD сигнала низкого уровня. Схема включения К583ВГ1 для генерации десяти управляющих синхроеернй приведена на рис. 5.26. Возможная схема соединения нескольких микросхем (каскадирование) для увеличения числа генерируемых синхросигналов Прерывание I 3anyai-\s CSpoc J\. кантрмь сбоев Коррекция mcmembi -Ucc

SS SS S7 -SB S3 SIO. Рис. 5.25. Временная диаграмма работы К583ВГ1 Рис. 5.26. Схема включения К583ВГ1 для генерации десяти синхросигналов

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||