| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Таблица 5.14

Таблица 5.15

косвенная адресация. Осуществляется посредством 3-раэрядного кода адреса, хранящегося в РУ; косвенная с нкрементироваиием и косвенная с декрементированнем адресации. Осуществляются посредством измеиеиня 3-разрядного кода РУ на +1 и -н1 соответственно. В битовых операциях используются три способа адресации битов, обрабал-ываемых в операциях (см. табл. 5.15): прямая адресация. Осуществляется подачей совместно с микрокомандой Э-разрядного кода адреса бита по магистрали LN0-LN2 (с записью в РН); косвенная адресация с инкрементированием. Осуществляется посредством увеличения на -Ы значения кода РАБ, по содержимому РАБ. Выбор РОН в битовых операциях осуществляется всегда по коду РУ. В байтовых операциях вход r является входом опроса схемы приоритета. При r=\\ происходит выдача признаков Я и £ по правилу Р = МО V М/ V М2 V ... V Л17, а £ = = Я, где МО-М7-выходные разряды схемы маскирования. При этом в РП записываетоя номер старшей (левой) I операнда. Если R=Oi, то в РП записывается OOOj и признаки R н Е обнуляются. В битовых операциях с кодом поля Я/ = = 11 вход R является входом разрещеиня нн-крементацни РАБ. Если r = 0, то РОН и РМС сохраняют свое содержимое, в репистры РМ, РП и РБ записываются нули, выходы р s3-Si- MBHi fnucmp номера SI у крапама

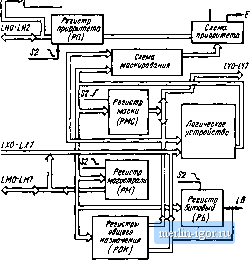

j\ Внутренние сигналы упраелени  Рнс. 5.16. Структурная схема К583ВМ1 и Е обнуляются. Если R==\ и РАБ=111, то записи в РОН и РМС не происходит. В регистры РМ, РП и РБ записываются нули, а выходы Я и £ принимают значение Я = 0 и £=1. Если -4 = 1 и РАБ =7111, то микросхема выполняет действия согласно принятой микрокоманде. Работа микросхемы оннхроииэнруется четырьмя управляющими синхрооигиалами S/- 5. Положительный перепад 5/ стробирует занесение информации в РМС, РВК, РН и регистры остаточного управления РУ и РАБ. Положительный перепад 52 стробирует занесение информации в РОН и РМС. Отрицательный перепад S2 стробирует занесение нн- ?ормацни в РМ, РБ и РП. Низкий уровень 3 разрешает выдачу информации на магистрали LB и LM. Низкий уровень S4 разреша-

Рис. 5.17. Формат микрокоманд микросхемы К583ВМ1 шо-шв, *5BHt BxoSLS, LM0-LM7, LX0-LX7 LYP-LY? 5J, вход LH0-LH7, LX0-LX7 >Z00hC Tq HOOOhc  Рнс. 5.18. Временная диаграмма работы К583ВМ1 >150нс >15.0нс >Z50m >,ЮОмс >150ис. У\. А ,.А- *300нс ет выдачу информации на магистраль LM. В зависимости от комбинации управляющих синхросигналов 5/ и S2 возможны четыре режима рабогы микросхемы: остаточного управления (S1 отсутствует); пропуска такта (S2 отсутствует); приостановки (5/ и S2 отсутствуют); нормальный режим (5/ и S2 присутствуют) Основные параметры KS83BM1 Номинальный ток инжектора /о = =/о1 +/о2 ......... 220 мА Потребляемая мощность Рсс при /о =220 мА......... 348 мВт Входной ток низкого уровня IiL при t/,i, = 2.4 В....... 0,2 мА Выходной ток высокого уровня, не более: для магистралей LM (0-7), LN (0-2), LB....... 0,45 мА для магистралей LY (0-7), Р. Е 0,05 мА Выходной ток низкого уровня loL, не более........ 20 мА Выходное напряжение низкого уровня UoL, ие более..... 0,4 В Время цикла Тс, ие менее . . . 1000 ис 5.5. Микросхема К583ХЛ1 Микросхема К583ХЛ1 - универсальный магистральный коммутатор (МК) байтовой информации, выполненный иа основе интегральной инжекциониой логики (№Л), предназначен для построения коммутаторов и мультиплексоров данных, буферных устройств хра- нення и логической обработки данных, устройств восстановления информации в системах с резервнрованнем. Условное графическое обозначение микросхемы приведено иа рнс. 5.19, назначение выводов дано в табл. 5.16, структурная схема показала иа рис. 5.20, формат микрокоманд микросхемы - на рис. 6.21, система микрокоманд - в табл. 5.17, временная диаграмма рабогы - на рис. 5 22. Микросхема обеспечивает выполнение следующих операций; межмагистральный обмен данными между четырьмя информационными магистралями в 12 направлениях; передачу информации нз магистралей в регистры; передачу информации из регистров в магистрали; логическую обработку байтовых данных; одновременный прием и одновременную выдачу байтовой информации на четыре магистрали данных; восстановление информации по мажоритарному принципу по двум из трех магистралей с выдачей результата на четвертую магистраль или записью в регистр четвертой магистрали. Структурная схема микросхемы К683ХЛ1, приведенная на рис. 5.20, содержит следующие функциональные узлы: четыре 8-разрядных двунаправленных магистрали L1(0-7) - L4(0-7) с выходом с открытым коллектором; четыре 8-разрядных буферных регистра RG1-RG4, синхронизируемых уровнем; Таблица 5.16

♦7 19 10 1Т , r.ie ♦ ц i7~ 3 4 S 6 оно: . 42 ♦4. Рис. 5.19. Условное графическое обозначение К583ХЛ1 четыре 8-разрядных логических устройства LU1-LU4; 13-разрядную магистраль управления S1- S13, одноразрядную магистраль синхронизации Логические устройства LU1-LU4 производят асинхронно выполнение логических операций над операндами, поступающими с магистралей L1-L4 в соответствии с табл. 5.17. Результат операции логических устройств поступает в выходные буферные регистры или ие-посредственно на магистрали L1-L4. Микросхема выполняет операции мажорирования байтовых данных для трех операн-юв по правилу *(А, В, C)={Af\B}\J{Bf\C)\J{AAC) Работа буферных регистров микросхемы RG1-RG4 синхронизирована одним синхросигналом R Отрицательный перепад уровней сигнала R стробирует занесение информации во все регистры данных RG1-RG4 одновременно Для микросхемы возможны два режима работы, задаваемые уровнем сигнала на входе R: без сохранения состояния магистралей В этом режиме при значении управляющего сигнала R - 0 в регистрах RGI-RG4 не происходит сохранения результата выполнения логических операций в LU1-LU4: с сохранением состояния магистралей В этом режиме при значении управляющего сигнала Л=1 регистры RG1-RG4 и магистрали L1-L4 соответственно сохраняют результат выполнения логических операций в логических устройствах LU1-LU4. £ Лкичккт истрвастЮ Регистр буферный JtotutecKM устройство (Ш2) Регистр Пуферный fc ПРВ2) у Лвгичеет устройстЮ (LU3) Регистр буферный (РВЗ) ± Логичесгое устройство (Ll/i) Регистр =t> буферный =J (Peif) Рис. 5.20. Структурная схема К583ХЛ1

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||