| |

|

Строительный блокнот Корпуса микропроцессорных микросхем 5.3. Мнкросхема К583Кт Микросхема К5вЗКП1 - коммутационный микропроцессор, выполненный по №Л технологии, предназначена для построения коммутаторов и мультиплексоров данных, буферных устройств хранения и логической обработки данных, устройств восстановления информации в системах с резервированием. Условное графическое обозначение микросхемы приведено иа рис. 5.Ill, назначение выводов - в табл. 6.9, структурная схема показана иа рнс. 5.12, формат микрокоманд - на рнс. 5.13, система микрокоманд - в табл. 5.10 и 5.11, временная диаграмма работы - на рнс. 5.14. Микросхема обеспечивает выполнение следующих операций: передачу информации из магистралей в регистры; передачу информации нз регистров в магистрали!; передачу информации между регистрами; межмагистральные лередачи; логическую обработку байтовых данных; операпш коммутации двухбайтовых данных; последовательный прием и одновременную выдачу до четырех байтовых данных; операции выдачи трехбайтовых данных из регистров на три магистрали, операции приема и выдачи четырехбайтовых данных; сравнение байтовых данных с выдачей признака равенства нулю; мажорирование байтовых данных нз трех регистров по принципу 2 из 3 с записью результата в три регистра; мажорирование байтовых данных из трех магистралей по принципу 2 из 3 с записью результата в один регисто. Структурная схема микросхемы, приведенная на рис. 5.12, содержит следующие функциональные узлы: Таблица 5.9

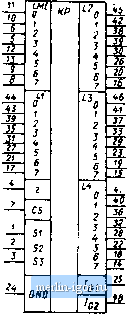

Рис. 5.11. Условное графическое обозначение К583КП1 7 Зак. 53 CS -SI SZ . S3.

Устройство управления LIWI-IH7I Внутренние сигналы управления Регистр вуферний (РБО i.3(0)-L3(7l Регистр буферный Ш01-Ш71 Регистр - буферный (РБЗ) Регистр магистральный (PMI) Регистр наtист -рольный (Рмг) Регистр маеис01-рольмый (РМЗ) Регистр буферный (РБЧ) Регистр магистральный iPMh) Регистр выборки кристалла (Рвк) Регистр донных (PAI) Регистр донных (РД21 Регистр ваяны* (РАЗ) Регистр данных (РА ) Рис. 5.12. Структурная схема К583КП1 четыре 8-разрядные двунаправленные магистрали данных Щ0~7)-14(0-7); четыре в-разрядиых буферных регистра РБ1-РБ4; четыре 8-разрядиых магистральных регистра РМ1-РМ4; четыре 8-разрядиых регистра данных РД1-РД4; 8-разряднюе логическое устройство; 8-<разрядную шнну микрокоманд LMIO- lmi7 и регистр м.икрокомаид; устройство управления; одноразрядный регистр выборки кристалла РВК. Логическое устройство выполняет логические операции иад операндами, содержащимися в регистрах РД1-РД4 идан поступающимм непосредственно с магистралей l1-L4. Оно имеет два входа (-4 я В) и выполняет одну из четырех логических операций в соответствии с Код ретина работы Коды адресов one -рандов и приемников результата кдп логического устройства Рнс. 5.13. Формат микрокоманд микросхемы К583КП1 табл. 6.11. При выполнении операций логическое устройство формирует признак нулевого результата иа выводе Z; если результат равен нулю, го Z==l. Результат операции логического устройства заносится в один из четырех или три из четырех регистров РМ1--РМ4. Микросхема выполняет операции мажорирования байтовых данных для трех операндов по правилу: *(а, Ь, c)={aAb)\/{af\c)\J{bc). К особенностям микросхемы относится наличие входа (выборки кристалла) записи информации в РВК. Если в РВК записана 1, то разрещается работа микросхемы, а если записан О, то никаких действий микросхема не производит. Работа микросхемы синхронизируется тремя онихросигналами; 5/, S2 и S3. Положительный перепад синхросигнала 5/ стробирует занесение м 1вро амаиды в РМК и сигнал Выбор кристалла в РВК. Положительный перепад синхросигнала 52 стробирует занесение информации в РД1- РД4 и РМ1-РМ4. Отрицательный перепад ейихроснгнала S2 стробирует занесение информации в РБ1-РБ4.

Примечание. X - состояние входа безразлично. Все микрокоманды выполняются прн CS=\. Низкий уровень снихрооигиала 53 разрешает выдачу информации на магистрали L1- L4 и вывод Z. Для микросхемы возможны четыре режима работы, задаваемые комбинациями 5/ и 52: режим остаточного управлеиия (5/ оохут-ствует). В этом режиме происходит многократное 1Исполнен е последней принятой микрокоманды; режим пропуска цикла (52 отсутствует). В этом режиме в каждом цикле принимается новая микрокоманда, но не исполняется; Таблица 5.11

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||