| |

Строительный блокнот Корпуса микропроцессорных микросхем

Рис. 5.8. Условное графическое обозначенне К583ИК1

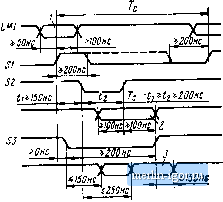

Регистры адреса, fPAO-FAJ) Регистр -J Sl/0epmu Регистр буферный Регистр, буферный (PLA) арифтти-песте Регистр микрокоманд (РНК) Регистр -указатель индекса, (PIAI Регистр длокироана лрерыдания (РВ) Регистр дней/него  Внутренние > упрадлйпщие сигналы Рис. 5.9. Структурная схема К583ИК1 косвенную, индексную и базовую адресацию ячеек ЗУ; четыре уровня вложенности подпрограмм; организацию условных и безусловных переходов в программах и микропрограммах; переход по внешнему прерыванию. Максимальная емкость адресуемой памяти 64К слов. Микросхема имеет четыре общих 16-разрядных регистра адреса РАО-РАЗ, обеспечивающих хранение адресов к памяти. Наличие 16-разрядного арифметического устройства обеспечивает выполнение различных арифмети-ческнх операций. Буферные регистры PLA, PLD, PD и PINT обеспечивают хранение информации в течение цикла при приеме и выдаче на соответствующие магистрали. Регистры РХ, PR, PIA, РВ, PZ образуют внутренний регистр состояния (PC) микросхемы, определяющий ее внутреннее состояние. Магистраль адреса LA обеспечивает вывод сформированного адреса к памяти. Магистраль данных LD обеспечивает возможность ввода адреса перехода, смещения нлн осуществления загрузюи/выгрузкн регистров адреса РАО-РАЗ. Схема формирования адреса регистров РАО-РАЗ выполнена так, что на входе устройства управления параллельно формируются четыре двухбитовых кода адреса выборки регистров РА; адрес из регистра микрокоманд; адрес из регистра нн- декса PIA; инкрементированный адрес из PIA; декрементированный адрес из PIA. Выборка одного из указанных адресов обеспечивается соответствующими разрядами микрокоманды. Работа микросхемы синхронизирована тремя синхросигналами: 5/, S2, S3 (рнс. 5.10). Синхросигнал 5/ стробирует занесение в РМК микрокоманды, синхросигнал S2 обеспечивает отработку принятой микрокоманды. Синхросигнал 55 стробирует выдачу информации нз микросхемы на магистрали LA, LD и выход INT. Во время исполнения принятой микрокоманды возможны четыре комбинации синхросигналов 5/, 52, которые позволяют получить четыре режима работы микросхемы. Нормальный режим (5/, S2 присутствуют). Каждый цикл принимается новая микрокоманда, которая затем исполняется. Режим пропуска цикла (S2 отсутствует). Каждый цикл принимается новая микрокоманда, но не исполняется. Режим приостановки (5/, 52 отсутствуют) Хранится последняя принятая микрокоманда, но не исполняется. Режим остаточного управления (5/ отсутствует). Происходит многократное исполнение последней принятой микрокоманды. Возможиость этих режимов работы обеспечивается тем, что регистр РМК стробируется синхросигналом 5/, а регистры РАО-РАЗ, Таблица 5.7

Примечания I. Константа 0002,6 является сигналом переполнения регистра PIA, формируется по -и при PIAW, и выдается иа магистраль LA. 2. Коистаита 0003,6 является сигналом переполнения регистра PIA. формируется по -1 при Р1А=002 и выдается иа магистраль LA. 3. Индекс регистра PAi определяется переменной XX нз поля П1; ( = МК (2-3). INT,X euXOSbllA, LII.INF  Рис. 5.10. Временная диаграмма работы К583ИК1 PD, PLD, PIA, РХ, РР, PZ, PINT - синхросигналом 52. Управляющий синхросигнал 55 может подаваться в произвольный момент времени и не связан никакими временными соотнощеннями с синхросигналами 5/, 52. Микросхема выполняет 112 микрокоманд. Формат микрокоманды имеет постоянную длину и занимает восемь двоичных разрядов, которые разбиты на два независимых поля: поле кода операции регистра состояния П1 (разряды О-3) и поле кода операции арифметического устройства П2 (разряды 4-7). Поле П1 определяет пять операций регистра индекса адреса PIA и управляет вводом и выводом информации через магистраль LD. Поле П2 определяет источники операндов, функцию арифметического устройства, запись результата в регистры РАО--РАЗ, управляет выдачей адресов на магистраль LA. Система микрокоманд К5вЗИК1 представлена в табл. 5.7 и 5.8. Основные параметры К583ИК1 Номинальный ток инжектора Iq = - 1в\ + /о2 ........ 280 мА Потребляемая мощность Рсс прн номинальном токе инжектора . . 336 мВт Входной ток низкого уровня IlL прн t L = 2,4 В, не более ... 0,2 мА Выходной ток высокого уровня 1он, не более: для магистрали ld, вывода INT........... 0,45 мА для магистрали LA..... 0,05 мА Выходной ток низкого уровня loL, не более........ 20 мА Выходное напряжение низкого уровня и Oh, не более..... 0,4 В Время цикла Тс, ие более . . . 1000 не

Примечания. 1. ЯД( - один нз регистров адреса РАО-РАЗ, адресуемый нндексрым регистром PIA. 2. Константа 0001 является первым адресом подпрограммы обработки внешнего прерывания и формируется в микрокомандах, реагирующих иа прерывание прн условиях PZ-li я РВ-О,. 3. Константа 0004 является признаком лог. О результата н формируется в микрокомандах с модификацией + (РА. 1); -f(P-4j, PD); +(PD, l)-f[.[P-4j (0-7), PD (8-15)J, 1];-(РЛ., 1) при условии P =l. 4. Прн формировании любых констант (0001, , 0002,в, 0003,6, 0004и) формируется признак IN1=U. * - операция склейки байтов, ** Микрокоманды на прерывание не реагируют.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||