| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Поле Л1 Разряды микрокоманды

Выполняемая функция Признак результата я п X я т а. К-ОК-1 2 X к й S о. ко К-1 са а. ко к\ X п К-ОК-1 Запись ff,в (OOie) {F+l)+C F- (S+l)+C F+S+C F + C F + C S+C S-j-C FAS FAS FAS FyS F\JS F\JS fes Fes Левый логический сдвиг (F + C) Правый логический сдвиг (F+C) Левый циклический сдвиг (F+C) Правый циклический сдвиг (F+C) Левый арифметический сдвиг (F+C) Левый логический сдвиг (S+C) Правый арифметический сдвиг (F+C) Правый логический сдвиг (S+C) Левый циклический сдвиг (S-f-C) Правый циклический сдвиг (S+C) Левый арифметический сдвиг (S+C) Правый арифметический сдвиг [S+C) Левый логический сдвиг {F + S+C) Правый логический сдвиг (F+S+C) Загрузка регистра режима Примечания. I. С - входной перенос. 2 В столбце Мнемоника микрокоманды в скобках дана мнемоника микрокоманды 3. /( - признак позиции микросхемы. Если К-1. то данные воспринимаются как данные воспринимаются как числа. 4. f - первый операнд, S - второй операнд. + + + + + + + + + + + + + 4--4- для с коды. если К=0, то

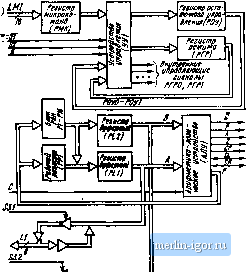

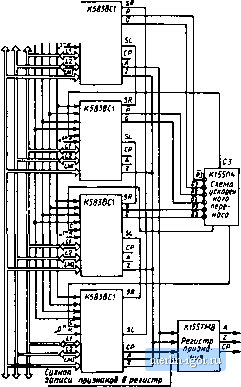

Примечания. I. Регистр-регистр (формат ЛЛ) - оба операнда 1аходятся в РОН нлн рабочем регистре PP. 2. Регистр-память (формат RL) - одни операнд хранится в РОН нлн РР, а другой принимается из магистрали L1 или L2. 3. Память-память (формат Lt) -оба операнда берутся из магистралей LI и L2 4. Поле П2 микрокоманды определяет источники операндов н приемник результата 5. X - состояние входа безразлично.  Прн запрете 5/, s2 (режим приостановки) новая микрокоманда не принимается, на регистрах сохраняется прежнее эиаченне. Если в предыдущей команде исполняется формат ll, rl, то может произойти смена признаков на выводах а, cp, z; если был формат rr, то смены признаков нет, Прн запрете 52 (режим пропуска такта) принимается новая мнкрокомаида, но ие исполняется, признаки на вывода1Х а, cp, z меняются. Если новая микрокоманда формата ll, то признаки и результат вырабатываются верные, однако записи результата не происходит, Так как признаки на выводах а, cp, z являются выходами комбинационной схемы, то для дальнейщей работы с ними их надо запомииать на внещнем регистре. Ми!крокома1Ида Загрузка регистра режима имеет особый формат, приведенный на рис, 5.6. Структурная схема объединения четырех микросхем К583ВС1 с применением схемы ускоренного переноса приведена на рнс. 5.7.

2 5 4 S 6 Т e 3 10 П 12 IZ 14 15 Рис. 5.3. Формат микрокоманд микросхемы К583ВС1 tcrlMHC >Шнс fi2 * Выходи U,L2 Выходы Ше SL.Sli Входы Входы C,SL,SK iBBOHC i220HC г-Шнс Рис 5.4. Временная диаграмма работы К583ВС1 к \S1 \S? \S3I \ S3?\ Рис. 5.5, Структура управляющего кода  Рис. 5.6. Структура микрокоманды Загрузка Рис. 5.7. Схема объединения четырех микрорегистра режима схем К583ВС1 Основные параметры К583ВС1 Номинальный ток инжектора 1о = =Igi + 1о2 ......... 300 мА Потребляемая мощность Рас при номинальном токе инжектора . . 360 мВт Выходной ток высокого уровня /он. ие более: для выводов П, Р, Z, CP, А 0,05 мА 5.2. Микросхема К583ИК1 Микросхема К5вЗИК1 предназначена для .построения устройств адресации ЗУ и устройств генерации последовательности кодов, выполнена по технологии интегральной инжек-циониой логики. для магистралей L}, L2, выводов SZ S/? ........0,45 мА Выходной ток низкого уровня loL, ие более........ 20 мА Выходное напряжение низкого уровня UoL, не более..... 0,4 В Время цикла Тс, не более . . . 1000 ис Условное графическое обозиачеиие микросхемы приведено на рис. 5.8, назначение выводов - в табл. 6.6, структурная схема показана иа рис. 5.9. Микросхема К583ИК1 обеспечивает: прямую и обратную последовательность адресации ячеек ЗУ;

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||