| |

Строительный блокнот Корпуса микропроцессорных микросхем

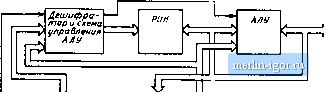

mmi mm mm mm 88USY СОНГ Sit KA CI сг СЗ Ck СТМГН INIUH SYH BI 03 Ok HPssini кшрцг нштз Рис. 4.10. Схема соединения микросхем МПК серии КР581 как указатели адреса, содержимое которых изменяется автоматически с заданным шагом, что позволяет обращаться к последовательно расположенным ячейкам памяти При этом автоматическое увеличение содержимого указателя при обращении к последовательно расположенным ячейкам памяти носит название автоиикремеитной, а уменьшение - автодекрементной адресации; как индексные регистры, содержимое которых прибавляется к индексному слову для вычисления адреса операнда. Использование автоинкрементного и автодекрементного методов адресации дает возможность организации стековой памяти. В качестве указателя стека может быть выбран любой программно доступный РОН. Общее число команд, включая команды с плавающей запятой, 72. 4.4. Микросхема КР581ВЕ1 Микросхема КР581ВЕ1 представляет собой микропроцессор с микропрограммным управлением, в функциональном отношении аналогичный базовому МПК серии КР581, состоящему из микросхем КР581ИК1, КР581ИК2, КР581РУ1, КР581РУ2. Она обеспечивает реализацию системы команд базового МПК (типа Электроника-60 ). Микросхема изготовляется по высокоточной п-канальной МДП-технологии с поликремниевыми затворами. Область применения: управление производством и технологическими процессами; сбор и обработка данных; решение научно-технических и экономико-статистических задач; проведение инженерно-конструкторских расчетов; моделирование и управление объектами в реальном масштабе времени. Условное графическое обозиачеиие КР581ВЕ1 приведено на рис. 4.11, структурная схема дана на рис. 4.12, функциональное назначение выводов показано в табл. 4.11, временная диаграмма входных и выходных сигналов - иа рис. 4.13. Общие характеристики КР581ВЕ1 обрабатыва- Разрядиость емых данных Управление Чиспо типов команд . . . Объем адресуемой памяти Число способов адресации . Число уровней прерывания Шина адреса и данных . . Быстродействие..... Система команд . . . . 8,16 бит Микропрограммное 64 64К байт 8 4 Совмещенная 330 тыс. операций/с Типа Электроиика-60 It *г Л Л. за . /f/R/f/ji WRRQl imRS3 INRRBt . RA SR COMP .33USY Mt MAZ ВАЗ BAi MAS BA5 DAI HAS DAB DAW DAtt DAtZ SA13 SAtk DAtS Mia MIS г? гб INRAK SYN DI WRBY BO 3Z 33 J± 35 JS Рис. 4.11. Условное графическое обозначенне КР581ВЕ1 Условно в структурной схеме можно выделить три основных функциональных блока: обработки информации, включающий в себя арифметико-логическое устройство, блок регистров общего назначения, дешифратор для адресации к РОН и схемы управления АЛУ; управления выполнением операций, включающий в себя контроллер микропрограммной последовательности (КМП), регистры команд и микрокоманд, логику управления вводом и выводом информации и обработки прерываний; микропрограммное постоянное запоминающее устройство (МПЗУ). Обмен информацией между основными блоками микропроцессора осуществляется по внутренней щнне микрокоманд. Работа микропроцессора происходит следующим образом. Команда, подлежащая испол-

буферные схемь/

Шина микрокоманд К С нема у управлений Контроллер микрапрограм -мной последовательности Рис. 4.12. Структурная схема КР581ВЕ1 iDAtS-DAO тнАк, t> SYN, DI, m/faf-тш, M,S/i, -I COMP, BeUSY м/в-мг/ нению, поступает на совмещенную щииу адреса и данных (DA15, ОАО на структурной схеме), заносится в регистр команд и поступает во внутреннюю шину микрокоманд. Начинается процесс вычисления адреса начала последовательности микрокоманд (микропрограммы), реализующей данную системную команду. Принятая команда по ШМК поступает далее иа расшифровку иа входы контроллера микропрограммной последовательности. Выходная информация КМП является функцией предыдущей микрокоманды, системной команды, слова состояния и управляющей информации Вычисленный адрес по ШМК поступает на входы ПЗУ микропрограмм (МПЗУ), которое формирует соответствующую данному адресу микрокоманду Емкость матрицы МПЗУ-1К 22-разрядных микрокоманд Младщие 18 разрядов микрокоманды направляются в ШМК для ее исполнения, старшие 4 разряда поступают в шину управления для управления внешними устройствами (Mt8-M2l)- Разряды О-15 микрокоманды поступают в регистр микрокоманд, где хранятся весь период ее выполнения. С выхода регистра микрокоманд микрокоманда поступает снова па вход КМП для участия в вычислении адреса следующей микрокоманды. Адресная часть микрокоманды поступает иа входы дешифратора для дешифрации содержимого блока ре гистров общего назначения, а код операции микрокоманды подается для расшифровки на логику управления АЛУ, которая вырабаты- вает сигналы, управляющие режимом работы АЛУ. Информация с выхода дешифратора поступает иа адресные входы блока РОН Выбранные из блока регистров общего назначения данные поступают иа обработку в АЛУ, которое параллельно обрабатывает два операнда. В качестве одного из операндов может использоваться литеральная часть микрокоманды. лт-мо BBUSY SH COMP lURAK

Рис 4.13. Временная диаграмма входных и выходных сигналов КР581ВЕ1

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||