| |

|

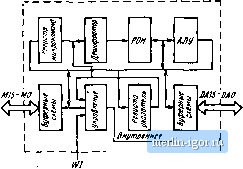

Строительный блокнот Корпуса микропроцессорных микросхем КР581 КР581-А КР581ВЕ1 Длительность тактового цикла, не Длительность тактового сигнала, не Время задержки между тактовыми сигналами, ис Время перехода тактового сигнала при включении и выключении, не Время перехода входных сигналов при включении и выключении, не thlc, tlhc thl , 90 20 600 125 20 300 70 5 4.1. Микросхема КР581ИК1 Микросхема КР581ИК1 предназначена для выполнения логических и арифметических функций иад системными данными. Условное графическое обозначение КР581ИК1 приведено на рис. 4.1, структурная схема даиа иа рис. 4.2, функциональное назначение выводов - в табл. 4.4, временная диаграмма показана на рис. 4.3. 21 Л. НА о VA2 ЛАЗ ЛА, SAS САб М М9 ЛАЮ ЛАП л А13 Л Aft Л А15 F 0 МО Mt Ml Ml Mi MS Ml MS MS Mio mTi mi3 31 36 Рис. 4.1. Условное графическое обозначение КР581ИК1 Таблица 4.4 Вывод 4-17, 22, 23 28-34, 36-44 46, 26, 47, 25 45 48 24 Обозначение Тип вывода Функциональное назначение выводов DA0-DA15 М15-М0 W1 С1-С4 Вход/выход Вход/выход Вход Входы Шина адреса и даииых. Используется мультиплексный режим работы информационных шин (передача адресных сигналов, команд и данных по одной шине) Шина микрокоманд. По шине микрокоманд организован обмен информацией между всеми микросхемами комплекта Сигнал Ожидание . При поступлении данного сигнала микросхема переходит в режим ожидания Тактовые сигналы от внешнего генератора Напряжение питания -t-12 В Напряжение питания +5 В Напряжение питания -5 В Общий Примечание. Источник питания СС1 используется.  управлете тггг- с1С2 сзс1> Рис. 4.2. Структурная схема КР581ИК1 Функционально микросхема включает в себя: арифметико-логическое устройство (АЛУ); регистры общего назначения (РОН); дешифратор; регистр микрокоманд и регистр-указатель для адресации к РОН; устройство местного управления, содержащее логическую матрицу дешифрации кода микрокоманды; буферные схемы. Выполнение всех операций осуществляется под управлением соответствующих микрокоманд (табл. 4.5). Система микрокоманд, реализуемая КР581ИК1, является важнейшей характеристикой МПК, достаточно универсальна и позволяет эмулировать произвольный набор системных команд. Для обеспечения возможности расширения системы команд или ее модификации и реализации всех преимуществ микропрограммного способа управления шина микрокоманд (ШМК) выполнена внешней по отношению к микросхемам МПК. Набор микрокоманд (табл. 4.5), реализуемых микросхемой, состоит нз следующих групп микрокоманд в соответствии с выполняемыми функциями: арифметические, логические, регистровые, сдвига, ввода, вывода, перехода, инкремента-декремента, управления. мо-ш I I I I I I I I сг а С! сг а I I I I I I I I

Арифметические Логические Регистр о- Рис. 4.3. Временная диаграмма работы КР581ИК1 Сложение литералов Сложение байтов Сложение слов Условное сложение байтов Условное сложение слов Сложение байтов с переносом Сложение слов с переносом Условное сложение слов Условное сложение чисел Вычитание байта Вычитание слова Вычитание байтов с переносом Вычитание слов с переносом Логическое умножение литералов Логическое умножение байтов Логическое умножение слов Логическое сложе ние байтов Логическое сложе ние слов Исключающее ИЛИ байтов Исключающее ИЛИ слов Логическое умножение прямого и инверсного байтов Логическое умножение прямого и инверсного слов Копирование флагов Загрузка флагов Загрузка регистра-указателя Пересылка байта Пересылка слова Условная пересылка байта Условная пересылка слова Загрузка регистра команд RaRa + ЛИТ RaRa + Rb RaRci-tRb+C RaRaRhC RaRa - Rh Ra<-Ra-Rh Ra*-Ra Rh С R R ~Rb-C ? .-?aЛлит RaRaARb Ra-R л Rh Ra RaMRh RoRaVRb RaRaMRb RaRaVRb Ra*-Ra Л Rh RaRa Л Rh R.,~Rb RaRb продолжение табл. 4.5 Окончание табл 4.5

Примечания I Ka ~ регистр с адресом ноля а микрокоманды; Нь - регистр с адресом поля 6 микрокоманды; ЛИТ - литерал; ШАД - шина адреса н данных. 2 Общее число реализуемых микрокоманд 91. Под временем цикла tc на временных диаграммах понимается промежуток времени между началом действия тактового сигнала С1 первого цикла и началом действия тактового сигнала С/ второго цикла. Обозначение выводов микросхем на ди;1Г-раммах принято в соответствии с условными графическими обозначениями и табл, 1.4. На рис 4.3 приняты следующие обозначения; Ввод - ввод информации по данному выводу или группе выводов во время .тепствия соответствующих тактовых сигналов; Вывод - вывод информации по данному выводу или группе выводов; Заряд - установление на данном выводе или группе выводов напряжения высокого уровня; 3-е сост. - во время действия соответствующих тактовых сигналов на данном выводе (группе выводов) устанавливается режим 3-го состояния. Эти обозначения приняты для выводов с совмещенными функциями ввода/вывода информации. Для выводов, выполняющих функции только входов нли только выходов, такие обозначения не приведены. Функцию заряда разрядов ШМК в МПК выполняют микросхемы КР581РУ1 - КР581РУЗ. Блок РОН имеет двухканальную (двухпортовую) структуру; при этом один из каналов (порт В) предназначен только для чтения, а второй (порт А) используется как для чтения, так и для записи информации. Порт Л регистрового блока связан с шиной адреса и данных ШАД, через эту шниу осуществляет-

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||