| |

|

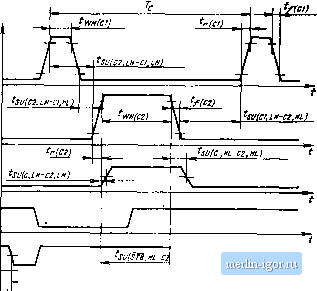

Строительный блокнот Корпуса микропроцессорных микросхем CI CZ  Рис. 3.72. Временная диаграмма работы КР580ГФ24 BBYIH. BESIN , tr(r:Brin,HL-srB, HL) isi/l/ruyJH.LH-STB.HL) lh) -}Jn(m) SUlHDr, LM/mL -C2, HL) Основные параметры микросхемы в диапазоне рабочих температур от -10 до 70°С при напряжениях питания t/cci = +5 В±5%, t/cc2=-f-12 В±5% приведены в табл. 3.55. 3.12. Микросхемы КР580ВК28 и КР580ВК38 Микросхемы КР580ВК28, КР580ВК38 - системный контроллер и буферный регистр данных, применяются в микропроцессорных системах на базе микропроцессора КР580ВМ80А для формирования управляющих сигналов и как буферный регистр данных. Условное графическое обозначение микросхем приведено на рис. 3.73, назначение выводов - в табл. 3.56, структурная схема показана иа рис. 3.74, временные диаграммы - на рис. 3.75. Микросхемы КР580ВК38 и КР580ВК28 отличаются лишь длительностью двух формнру-емых управляющих сигналов: WR и WR10. Системный контроллер формирует управляющие сигналы по сигналам состояния мик- ропроцессора при обращении к ЗУ: RD и WR. при обращении к УВВ: RD 10 и WR 10, INTA, а также обеспечивает прием и передачу 8-разрядиой информации между каналом данных микропроцессора по выводам D7-DO и системным каналом по выводам DB7-DBO-Системный контроллер состоит из двунаправленной буферной схемы данных, регистра состояния и дешифратора управляющих сигналов. Восьмиразрядная параллельная трехста. бильная буферная схема данных принимает информацию с канала данных микропроцессора по выводам D7-D0 и передает в регистр состояния информацию состояния, на системный канал данных по выводам DB7- DBO выдает данные в цикле записи по сигналу В цикле чтения по сигналу RC буферная схема принимает данные с системного канала по выводам DB7 и DBO и передает по выводам D7-D0 на канал данных микропроцессору. Регистр состояния по входному сигналу STB фиксирует информацию состояния мик-

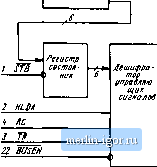

2 3 4 5. 7, 9, п. 13, 16, 18, 20 6, 8. 10 12,15,17 19, 21 24 25 26 27 28 HLDA TR RC DB4, DB7, DB3. DB2, DBO, DBl, DBS, DB6 D4, D7, D3, D2, DO, Dl, DS, D6 BUSEN INTA RD RD 10 WR WR 10 Вход Вход Вход Вход Выход/ вход Вход/ выход Вход Выход Выход Выход Выход Выход Вход Стробирующий сигнал стояния Подтверждение захвата Выдача информации Прием информации Канал данных системы Канал данных микропроцессора Общий Управление передачей данных и выдачей сигналов Подтверждение запроса прерывания Чтение из ЗУ Чтение из УВВ Запись в ЗУ Запись в УВВ Напряжение питания --5В 15 п IZ < IL гв

il 23 Рис. 3.73. Условное графическое обозначение КР580ВК28, КР580ВК38 ропроцессора в такте Т1 каждого машинного цикла микропроцессора. Дешифратор управляющих сигналов формирует один из управляющих сигналов в каждом машинном цикле: при чтении ЗУ - W, при записи в ЗУ - WR, при чтении из УВВ - RD 10, при записи в УВВ - WR 10, при подтверждении запроса прерывания ~ сигнал INTA. Асинхронный сигнал BUSEN управляет выдачей данных с буферной схемы и управляющих сигналов с дешифратора: при напря-жении низкого уровня на входе BUSEN буферная схема передает данные и формируется одни из управляющих сигналов; при напряжении высокого уровня все выходы микросхемы переводятся в высокоомиое состояние Напряжение высокого уровня на входе HLDA переводит выходы RD, RD 10, INTA в пассивное состояние (напряжение высокого уровня) и блокирует передачу информации через буферную схему данных. Управляющие сигналы WR и WR 10 формируются в цикле записи в микросхеме КР580ВК28 по сигналу TR, в микросхеме КР580ВК38 - по сигналу STB При работе с микропроцессором КР580В.М80А системный контроллер в цикле подтверждения запроса прерывания формиру- 6 Зак. 53 ет три сигнала INTA для приема трех байтов команды CALL от контроллера прерывания КР580ВН59. S по /7 BI 12 вг Ю BJ S Bi IS т 21 06 б 17 двунаправленная буферная схема данных ВВО а B8I 16 тг II BBS 18

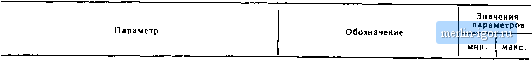

Рис. 3.74. Структурная схема КР580ВК38 КР580ВК28,  Выходной ток высокого Уровня: для выходов D7-DO, мкА для остальных выходов, мА Выходное напряжение высокого уровня на выходах D7~D0, В Выходной ток низкого уровня, мА: для выходов D7-D0 для выхода INTA для остальных выходов Ток потребления, мА Входная емкость, пФ Выходная емкость управляющих выходов/выходов DB7-DB0, пФ Длительность сигнала STB, не Время установления сигналов RD. RD 10. INTA относительно сигнала STB. не Время сохранения сигналов RD. RD 10, INTA относительно сигнала RC. не Время установления входной информации относительно сигнала STB, не Время сохранения входной информации относи тельно сигнала STB, не Время сохранения сигналов RD, RD IO, INTA относительно сигнала HLDA, не Время установления информации на выходах D7-DO относительно сигнала RC в цикле чтения, НС Время задержки информации на выходах D7-D0 относительно входной на выводах DB7-DBO в цикле чтения, не Время сохранения информации на выводах DB7- DBO относительно сигнала HLDA, не Время сохранения информации на выводах D7- DO относительно сигнала RC в цикле чтения, не Время установления и сохранения сигналов WR нли WR 10 относительно сигнала TR, ис Время установления сигналов WR или WR 10 относительно сигнала 576, не Время задержки информации на выводах DB7- DBO относительно информации на входах D7- Do в цикле записи, не Время установления информации на выводах DB7-DBO относительно сигнала BUSEN, не Время установления информации на выводах DB7-DBO относительно сигнала HLDA в цикле чтения, НС Примечание ниях к табл 3.8 а: С, WI (STB) SU{RD, HI STB. HL) VJrd. LH-RC, HL) sL (D-STH. HL) sn(U -STR. LH) V(RD, LH-Hl UA. HI) si(l) RC I H) d(D -DH) s(j{DB HLDA. LH) sa{D-RC. HL) hu(WR~TR. HLJLH) SU{WR-.STB. HL) d(DB-D) smDB-BUSE\. HL/LH) *SU(DBHLDA, LH) 22 20 5 20 5 2 5 10 60 30 25 45 45 45 60 40 Пояснения к буквенным обозначениям временных параметров приведены в примеча- ♦ Только для микросхемы КР580ВК38

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||