| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Рис. 3.65. Пример реализации интерфейса иа микросхемах КР580ВК91А, КР580ВА93 т т ш т м О Ж wit cs ввеа Шн CLOCK ПЕЗЕТ тт ши BAV ЯШ ATN Ш

ч>

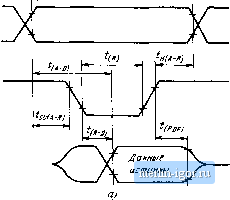

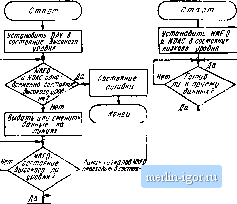

ДОЙ, a обычно следующее за ним сообщение РРЕ - неопределенной вторичной командой. Подробно эта процедура описана в подпара-графе Протокол параллельного опроса . Таблица 3.50 Регистр Конец последовательности (EOS). Свойства регистра EOS позволяют применять его вместо вспомогательной команды Посылка Е01- . В этот регистр можно Параметр Обозначение Значения параметров Режим измерения Входное напряжение низкого уровня, В Входное напряжение высокого уровня, В Выходное напряжение низкого уровня, В Выходное напряжение высокого уровня, В Выходное напряжение высокого уровня для прерывания, В Ток утечки на входе, мкА Выходной ток в состоянии выключено , мкА Ток потребления, мА 0H-INT -0,5 2,0 2,4 3,5 Ucc+0.5 0,45 ±10 ±10 / , = 2 мА (для вывода TRI I oL * 1 . -0,4 мА (для вывода SRQ Iq = -0,15 мА) -0,4 мА -0,05 мА и, от О В до U(-(-и а - 0,45 В он он поместить 7- или 8-битовый байт (в коде ASCII или двоичном коде соответственно) для индикации конца блока или чтения. Тип этого байта выбирается битом At во вспомогательном регистре А- Если микросхема КР580ВК91.А является приемником и битом Лг разрешается END CS/HS;  Шипа данных (дыдод данных) шина донных д, мощно (.вдодданных) изменять ЩА-W) H(D-W) XДанные -JМанные истинны \ нотно \изменять дПЕа (ПНПЯ!*) ЛАСК Рис. 3.66. Временные диаграммы работы KP580BK9IA в режимах Цикл чтения (а), Цикл записи (б), Цикл ПДП (в) Imms) Ш7-т08 Истинно Не истинно MFJ! ша(5н) тЕа(Ан) Ш *(HDnvl) ffHSHKJ) Истинно Рис. 3.67. Временная диаграмма процесса синхронизации информационного обмена для микросхемы КР580ВК91А по приему £05 , то всякий раз, когда байт в регистре Ввод данных совпадает с байгом в регистре £05, в регистре Состояние прерывания 1 будет генерироваться прерывание END. Если микросхема KP580BK9IA - передатчик и битом Лз разрешается Вывод EOI при посылке EOS , то на выводе EOI будет истинное значение при посылке следующего байта данных всякий раз, когда содержимое регистра Вывод данных совпадает с содержимым регистра £05. Процедура сброса. Микросхема КР580ВК91А сбрасывается в состояние инициализации либо импульсом, поданным на вывод RESET микросхемы, либо вспомогательной командой Сброс микросхемы (записью в регистр Вспомогательный режим кода 00000010). Импульс сброса (или местная команда сброса) вызывает следующие состояния: местное сообщение роп, определяемое стандартом, удерживается истинным до разблокировки состояния инициализации; очищаются регистры Состояние прерывания (но не регистры Разрешение прерывания ) ; очищаются вспомогательные регистры А и В; очищается регистр Режим последовательного опроса ; сбрасывается флаг параллельного опроса; сбрасывается бит EOI в регистре Состояние адресации ; Nf во внутреннем счетчике устанавливается на 8 МГц. Эта установка вызывает генерирование в SH самой длительной задержки Г (16 мкс для частоты синхросигнала 1 МГц); посылается местное сообщение rdy Состояние инициализации (разблокируется командой Немедленное исполнение роп* (записью кода 00000000 н регистр Вспомогательный режим ). Предлагаемая последовательность инициализации: 1. Подать импульс сброса или послать вспомогательную команду Сброс микросхемы . 2. Установить требуемые начальные условия (режимы) путем записи в регистры Разрешение прерывания , Режим последовательного опроса , Режим адресации , Адрес 0/1 , E0S . Необходимо также инициализировать вспомогательные регистры .4 н 8 и внутренний счетчик. Акцептор  , Штатдить NeFB , б состоякое бысо- кого уробии ш Высокого 1/робкк только тгбо, когда See акцепторы гвто-  Устанобить ВЛу I состоите низко-го уробия Данные действительны. MOHfHO принимать  Рриеп байта данных Установить PAV б состоиние высокого цробкк С зтого момента  данные считаются небей-ствительными. Конец Установшь НвГб в состояние низко го уровня  Рис. 3.68. Структурная схема алгоритма процесса синхронизации Парамеф Обозначение Время установления сигнала RS, относительно сигнала /?D. не Время сохранения сигна-ла RSx после сигнала RD, нс Длительность сигнала RD. нс Время от сигнала до установления истинных данных, нс Время от сигнала RDhl до установления истинных данных, нс Время от сигнала RDlh до снятия данных, ис Время от сигнала RDhi (или WRhl) до сигнала DREQhl, не Время от сигнала RDhl до установления истинных данных на выводах D0-D7. нс Время установления сигнала RS, относительно сигнала WR, ис Время сохранения сигнала RS, относительно сигнала WR. нс Длительность сигнала WR. не Время установления дан-ных относительно сигнала WR. нс Время сохранения данных относительно сигнала WR. нс Н(4 -Н) (a-d) (r-d) {rijf) {DKUR4) sbia-vt) Н{А -W) S О I CO с p.- (250) (100) 0(60) (130) (200)* 170 130 Время or сигнала dackhl до сигнала rdhl не более 50 не. 3. Послать вспомогательную команду Немедленное исполнение роп для разблокировки состояния инициализации. 4. Если используется РР2 режима параллельного опроса, то может посылаться местное сообщение Ipe, разрешая микросхеме КР580ВК91А реакцию параллельного опроса на присвоенной линии (см. Протокол параллельного опроса ). Использование ПДП. Для работы с ПДП микросхема КР580ВК91А может объединять-

|