| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Продолжение табл. 3.43

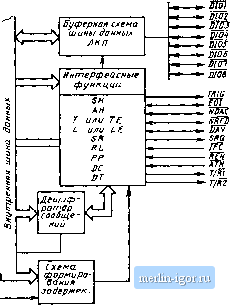

Примечания. 1. Параметры входных сигналов, имеющие размерность времени, измеряются прн следующих условиях; входное напряжение высокого уровня 2,4 В, входное напряжение низкого уровня 0,45 В. 2. Параметры выходных сигналов, имеющие размерность времени, измеряются непосредственно иа выводах микросхемы при емкостной нагрузке. Емкость нагрузки с учетом емкости монтажа и входной емкости измерителя не должна превышать 160 пФ дл>1 шииы данных и 50 пФ для остальных выводов. Измерения производятся по уровням 2,0 В н 0,8 В для напряжений высокого и низкого уровней соответственно. воспроизведения и сбрасывается командой Прекращение воспроизведения нлн Сброс ; DV - Недогрузка ПДП . Устанавливается всякий раз, когда возникает недогрузка данных при пересылке в цикле ПДП. При обнаружении DV действие ПДП останавливается, экран бланкируется вплоть до окончания обратного хода кадровой развертки. Флаг сбрасывается после чтения состояния; F0 - Переполнение FIFO*. Сбрасывается после чтения состояния. Основные параметры микросхемы при напряжении питания 5 В±5% и в диапазоне температур от -10 до +70°С приведены в табл. 3.43. Временные диаграммы работы микросхемы для различных сигналов приведены на рис. 3.59, а--м. 3.10. Микросхема КР580ВК91А Микросхема КР580ВК91А - микропроцессорно управляемое устройство, предназначено для сопряжения микропроцессоров и однокристальных микро-ЭВМ с линией коллективного пользования информационио-измери. тельной системы типа 2 - ЛКП ИИС-2 (стандарт СЭВ СТ СЭВ 2740-80). Микросхема осуществляет связь между ЛКП и устройствами, управляемыми микропроцессором. В ее функции входит передача данных, протокол синхронизации обмена, процедуры адресации приемников/передатчиков, очистка и запуск устройств, запрос обслуживания, последовательный и параллельный опросы, а также все остальные функции интерфейса, за исключением функции контроллера. Условное графическое обозначение микросхемы приведено на рис. 3.60, назначение выводов - в табл. 3.44. Структурная схема КР580ВК91А показана на рис. 3.61. Она состоит из буферной схемы щины данных микропроцессора; логической схемы чтения/записи/ПДП, прерываний, восьми регистров записи; восьми регистров чтения; схемы формирования задержек; дешифратора сообщений; логической схемы, реализующей интерфейсные функции; буфер ной схемы щины данных ЛКП; внутренней щины данных. Буферная схема шииы данных микропроцессора представляет собой двунаправленный 8-разрядный регистр с тремя состояниями вы- водов и служит для сопряжения внутренней шины данных микросхемы с микропроцессорной шиной данных системы. Ее работой управляет логическая схема чтения/записи/ПДП. Логическая схема чтения/записи/ПДП и прерываний управляет процессом двунаправленного обмена информацией между микросхемой и центральным процессором Декодируя внешние управляющие сигналы, она адресует информацию от процессора в соответствующие регистры записи микросхемы, а пн- Таблица 3.44

формацию из регистров чтения микросхемы- на шину данных процессоров. Эта же схема управляет режимом ПДП, переводит шину данных микропроцессора в состояние выключено и вырабатывает сигналы прерывания (рис 3.62). Восемь регистров записи (0W-7W) позволяют разработчику посредством записи в них определенных кодов реализовать режим микропрограммирования микросхемы KP580BK9IA. Содержимое этих регистров оп ределяет режим работы как собственно микросхемы КР580ВК91А, так и всего интерфейса в целом. Восемь регистров чтения (OR- 7R) обеспечивают разработчику возможность посредством их считывания микропроцессором осуществлять контроль за состоянием ЛКП, режимом работы устройства и состоянием шин Схема формирования задержек формирует необходимую задержку Гь определяемую стандартом, для установления истинных данных на ЛКП (шина D101-D108). Дешифратор сообщений декодирует команды и сообщения, поступившие с ЛКП. и в соответствии со стандартом переводит микросхему в требуемый режим работы Одновременно с этим дешифратор сообщений управляет функциями интерфейса, вырабатывает управляющие сигналы для логики ПДП. Примечание Все си1налы на выводах микросхемы КР580ВК91А определены в положительной логике Однако стап дарт определен в отрицательной логике иа 16 сигнальных линиях Поэюму входные данные инвертируются от DO 07 к DI01 - DI08, что позволяет применять иеиивертирующне шинные драйверы III vz ЛЗ BS RSO KSI R$2 1 IW cs BKEQ CLOCK TRIB П103 BIO* BIOS DIOl Dias r/Kl NNFD NDAC Рис. 3.60. Условное графическое обозначение КР580ВК91А DB3 Dei-* m Ш - CS - mcn- ff5ff -Л57 -Я52 -fffSfr-ГЫГ~т буферная схема шины данных микропроцессора чг-v -Могичес-) коя схема чтения, записи, ПДП, преры -Ваний

CLOCK  Рис. 3.61. Структурная схема КР580ВК91А Логическая схема, реализующая интерфейсные функции SH, АН, Т, ТЕ, L. LE, SRQ, RL, DT, DC в соответствии с заложенной в регистры 0W~7W информацией, обеспечивает выполнение алгоритма работы интерфейса. Буферная схема щины данных ЛКП представляет собой двунаправленный 8-разрядный регистр с тремя состояниями выводов и служит для сопряжения внутренней щины данных микросхемы с драйверами. Работой этой схемы можно управлять со стороны микро- I Системная шима микропроцессора I Контроллер I ПДП (при неоВход. мести]

Рис, 3.62, Вариант использования микросхемы КР580ВК91А процессора посредством записи определенных кодов в регистры записи нли воздействием команд управления с ЛКП. Внутренняя щина данных микросхемы обеспечивает передачу информации от регистров записи к логическим схемам интерфейсных функций и на ЛКП, передачу данных от ЛКП к микропроцессору. Интерфейс информационно-измерительной системы ИИС-2, На рнс. 3.63 показана структурная схема линии коллективного пользования ИИС-2 с подключенными устройствами, в табл. 3.45 приведены состояния функций интерфейса, в табл. 3.46 - принимаемые и посылаемые сообщения ИИС-2. Модифицированные диаграммы состояний КР580ВК91А приведены в конце гл. 3. Выводы микросхемы выполняют следующие функции: Шина данных микропроцессора - выводы порта, подключаемые к щнне данных микропроцессора. Адрес регистра - входы выбора регистра. Подключаются к трем немультиплексирован-иым линиям адресной шииы микропроцессора. Выбирают, какой из восьми внутренних регистров чтения (записи) будет считан (записан) при исполнении RD (WR). Выбор микросхемы - прн низком уровне разрешает чтение нли запись в регистр, выбранный посредством RS0-RS2. Чтение - стробирующий сигнал, по низкому уровню которого содержимое выбранного регистра считывается центральным процес-

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||