| |

|

Строительный блокнот Корпуса микропроцессорных микросхем режим чтения ПД - обеспечивает передачу данных из памяти в периферию; режим записи ПД - обеспечивает передачу данных из периферии в память, режим проверки ПД - не включает передачу данных. Канал ПД в режиме проверки не генерирует сигналы управления rd. wr, rd 10, WR 10, что предотвращает передачу данных. Однако в каждом цикле ПД микросхема осуществляет управление системной шиной и подтверждает запросы периферии Периферия может использовать сигналы подтверждения для разрешения внутреннего доступа к каждому байту в массиве данных для того, чтобы выполнить некоторые операции проверки. Например, массив циклов проверки ПД может следовать за массивом циклов чтения ПД (из памяти в периферию) для того, чтобы разрешить периферийному устройству проверить вновь поступившие данные. После окончания запрограммированного числа циклов ПД, характеризующегося выработкой сигнала ТС, возможны следующие виды работы дальнейшее наращиваиие адреса путем прибавления 1 в каждом последующем цикле ПД, блокировка канала ПД (режим КС-стоп ); повторение ранее выработаииого массива адресов (режим автозагрузки), Прн наличии двух и более запросов будет обслуживаться периферия с наивысшим приоритетом. Вид приоритета устанавливается в процессе программирования Имеется два вида установки приоритета фиксированный, когда канал О имеет наивысший приоритет, а канал 3 -самый низкий; циклический сдвиг приоритета, когда после каждого цикла ПД приоритет каждого канала изменяется. В процессе функционирования микросхемы путем программирования РгР можно заблокировать (замаскировать) запрос любого канала В процессе функционирования в составе микропроцессорной системы микросхема может находиться в одном из следующих состояний исходное, программирование; ожидание, обслуживание. В исходное состояние микросхема устанавливается после включения путем подачи на ее вход SR сигнала Установка В этом состоянии маскируются запросы всех каналов ПД, а трехстабильные буферные схемы системной шииы АО-A3 переводятся в состояние приема информации В состоянии программирования микросхемы микропроцессор по системным шинам данных DO-D7 осуществляет запись в соответст вующие регистры микросхемы исходных данных (начальные адреса и число циклов) и инструкции, определяющей режим работы микросхемы при циклах ПД При этом адресат приема информации микросхемой определяет ся кодом на системных шинах АО-A3 В оостояни ожидания микросхема находится от момента окончания программирования до получения сигнала Подтверждение запроса захвата HLDA или в промежутках между массивами циклов ПД в отсутствие запросов ПД В состоянии ожидания осуществляется прием сигналов DRQ и вырабатывается для микропроцессора сигнал Запрос захвата HRQ В этом состоянии системные шины находятся под управлением микропроцессора После получения от микропроцессора сигнала HLDA при наличии сигнала запроса DRQ микросхема вырабатывает сигнал DACK и переходит в состояние обслуживания В этом состоянии системные шины находятся под управлением микросхемы, которая осуществляет один из запрограммированных режимов ПД и генерирует набор управляющих сигналов, ие обходимых для осуществления обмена данными между памятью и периферией Регистры микросхемы загружаются или с них считывается информация, если процессор выполняет команду записи или чтения путем обращения к микросхеме КР580ВТ57 и к соответствующим регистрам внутри микросхемы Для этого процессору необходимо выдать со ответствующие сигналы записи или чтения WR 10, RD 10 и на системные адресные шины выдать адрес регистра микросхемы В это время на шину данных подается необходимая информация для записи в регистры или же через шину данных читается информация из микросхемы Для установки состояния программирования необходимо также на микросхему подать сигнал CS - Q, получаемый обычно путем декодирования всех или .некоторых старших 112 разрядов адреса А4-А15 (в зависимости от системной организации памяти и устройств ввода/вывода) Вход WR 10 (или WR при об щем поле памяти и УВВ) указывает на запись в регистры микросхемы, а вход RD 10 (или RD) - на чтение из регистров Разряд A3 позволяет раз.тичить регистры каналов при Л3=0, а при Л3=1-регистр установки режима (работает только на запись), и регистр состояния каналов (работает только иа чтение) Три младших разряда АО-А2 указывают конкретный регистр канала Если адресуется регистр установки режима или регистр состояния каналов, то разряды АО-А2 должны быть установлены в О Когда адресуется регистр канала, разряд АО позволяет различить регистры адреса ПД (при Л = 0) и числа циклов (при Л=1) Разряды А1, А2 позволяют определить номер канала Коды выборки регистров приведены в табл 3 25 В связи с тем, что регистры канала являются 16-разрядными, для их загрузки или чте ния необходимо два программных командных цикла В микросхеме имеется триггер, который автоматически переключает цепи во время выполнения операции чтения или записи Этот триггер определяет доступ к старшему или младшему байгу регистра Сбрасывается триггер путем подачи сигнала н вход SR, а гакже

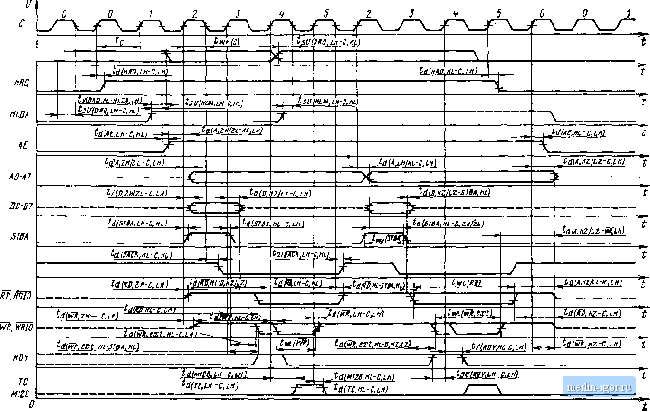

П р и .VI еI а и и е A3 анюза! руэка. УЗ - удлиненная запись. ЦСП -циклический сдви! приоритетов. РК ~ разрешение канала. ФОД ~ флаг обновления данных; АО - AI5 - начальный адрес, C0-CI3 -число циклов, чт -Ч1ение ПД. ЗП - запись ПД. ВЛсс Ш Up isVlCS.HiRVll.HL} UlCS,L -:!!C,LI) tvli.HL/LH-m}j.K) Рис. 3.33. Временные диаграммы работы КРЬ80ВТ57 в режиме программирования при записи \а) и чтении (б): 6н=-2,0 В: 6,.=-0,8 В  Рис. 3.34. Временная диаграмма работы КР580ВТ57 в режиме прямого доступа. Цифры О-5 соответствуют внутренним состояниям микросхемы

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||