| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Программирование микросхемы на требуемый режим работы производится путем занесения в соответствующие регистры слов инструкций режима, синхроснмволов (для оин-хроиного режима) и команд. Форматы и со- Таблица 3.11

Примечания 1 Если а процессе работы передатчика в регистр записывается команда DO Передача информации невозможна нлн на вход RTS подается напряжение лог. 1, запрещающее передачу информации, то УСАПП не прекращает передачу до тех пор, пока все данные, записанные в буферных схемах ввода/вывода н передатчике, не будут переданы полностью 2 УСАПП позволяет выполнять команды DO Передача информации возможна н D2 Прием информации возможен одновременно или раздельно 3 Команда D3 Пауза действует как в асинхронном, так и в синхронном режимах и указывает на паузу во время передачи данных Вывести микросхему из состояния Пауза можно внешним снгна лом SR. командой D6 Программный сброс или командой D3 Пауза 4. Команду D4 Сброс триггеров ошибок в исходное состояние необходимо записывать каждый раз перед программированием команды D2 Прием ии формации возможен или одновременно с ее программированием 5 Команда П7 Поиск сннхросимволов используется только в синхронном режиме н должна программироваться одновременно с командой D2 Прием информации возможен

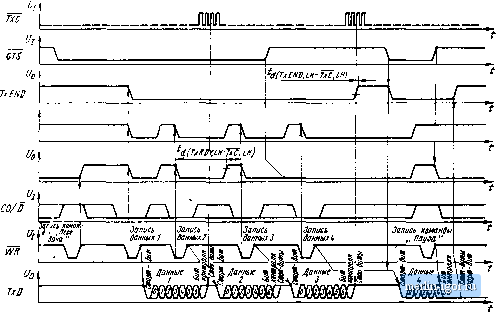

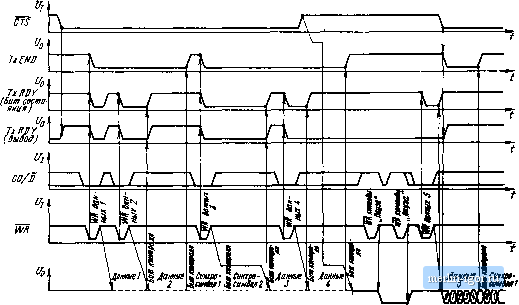

Примечание. X - состояние входа безразлично держание инструкции режима приведены на рнс. 3.7, команды - в табл. 3.11. Последовательность программирования инструкции команды, инструкции режима и сннхросимволов для подготовки микросхемы к работе приведена в табл. 3.12. Процесс про-граммнровання в целом асинхронен относительно сигналов RxC н ТхС, однако запись ннст-рукцн;. режима для асинхронного режима 1 : 1 должна производиться только в положительном полуперноде сигналов RxC н ТхС. Прн занесении в микросхему управляющих слов или данных, а также прн чтении состояния на вход С должны поступать импульсы сннхроннзацнн. Время восстановления между операциями записи (WR) в асинхронном режиме 8Тс, в синхроином режиме 16Тсьс Данные D0-D7 записываются в буферные схемы ввода/вывода после перехода сигнала WR из состояния низкого уровня в состояние высокого уровня через 2Гс. При чтении состояния входные сигналы CTS и DSR устанавливаются за 8Тс до перехода сигнала RD из состояния высокого уровня в состояние низкого уровня. Состояния, указанные в последних двух пунктах табл. 3.10, соответствуют высокоом-ному состоянию буферных схем ввода/вывода. В это время операции ввода/вывода не производятся. При передаче/приеме информации микросхема устанавливается в исходное состояние сигналом SR. После записи инструкции режима, синхро-символа (оннхроснмволов) и инструкции команд она переходит в один из пяти основных режимов работы. 1. Асинхронная передача. Временные диаграммы для данного режима приведены на рнс. 3.8. После записи в микросхему данных в параллельном формате происходит автоматическое присоединение к каждой посылке старт- (Sum состояния)  {вывод) 3 8 Временная диаграмма работы КР580ВВ51А в режиме асинхронной передачи бита и стоп-бита Бит контроля четности (если он запрограммирован) вводится перед битами останова и может иметь нулевое или единичное значение Если в инструкции команды в разряд DO записана 1 и на входе CTS устанавливается напряжение низкого уровня, то информация в виде последовательного потока данных подается на вывод TxD с частотой, кратной 1 1, 1 16 или 1 64 части частоты синхронизации передатчика (как определено инструкцией режима) Если микросхема не содержит инфор мацию 1ЛЯ передачи, то на выходе TxD устанавливается напряжение высокого уровня Если в инструкции команды запрограммирован режим пауза , то на выходе TxD устанавливается напряжение низкого уровня 2. Асинхронный прием. Временная диаграмма для данного режима приведена на рис 3 9 Напряжение высокого уровня на входе RxD свидетельствует о том, что в данный момент нет приема информации Если УСАПП запрограммирован инструкцией режима на асинхронный прием, то появление на входе RxD напряжения низкого уровня свидетельствует о приходе старт-бита Истинность этого бита проверяется вторично стробирова нием в его середине Если наличие напряжения низкого уровня на входе подтверждается, то запускается счетчик битов, который позво ляет определять конец битов данных, бит контроля (если контроль запрограммирован) и стоп-бит С другой стороны, если при вторичной пробе обнаруживается напряжение высокого уровня, то приемник переходит в исходное состояние Схема управления и сиихроиизации приемника предохраняет от ошибочного запуска счетчика битов, если на выводе RxD присутствует напряжение низкого уровня, вызванное командой D5 Пауза Регистр приемника обнаруживает паузу я на выводе SYNDETIBD устанавливается напряжение высокого уровня Если есть ошибка в принятых данных, то триггер ошибки четности устанавливается в единичное состояние. Если при анализе окажется, что стоп-бит в состоянии низкого уровня, то триггер ошибки стоп-бита устанавливается в единичное состояние Стоп-бит сигнализирует о том, что данные находятся в приемнике Принятые данные передаются через внутренние шины данных в выходной регистр данных, и тогда иа выходе RxRDY появляется напряжение высокого уровня, сигнализируя о готовности к считыванию Если предыдущий символ (данные) ие был передан в микропроцессор, то принятый символ заменяет его в буферных схемах ввода1(вывода и триггер ошибки переполнения устанавливается в единичное состояние (т е предыдущее число теряется) Триггер ошибки переполнения так же установится в единичное состояние, если чтение данных произойдет в момент записи данных из регистра приемника в выходной регистр данных буферных схем ввода вывода (в этом случае предыдущие данные также те ряются) Наличие ошибок в триггерах не останавливает работу микросхемы Триггеры ошибок сбрасываются инструкцией команды в исходное состояние smer/ Лд Триггер muSm переполнения GO/S <е(лхш,ш-лхс,сн) Запись команды..Прием Запись триггера , Пауза коман! ..Clpoc ашидок и вались команды Чтение ванных 1 Данные 1 Данные2 mmmmmmmmBmmmmBi Чтение ванных 3 Данные J § ..Падза Рис 3 9. Временная диаграмма работы КР580ВВ51А в режиме асинхронного приема  Рис. 3.10. Временная диаграмма работы КР580ВВ51А в режиме синхронной передачи

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||