| |

Строительный блокнот Корпуса микропроцессорных микросхем

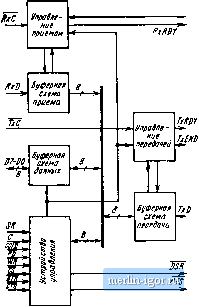

Примечания. 1. Символы LH(HL), ZH(LZ) и HZ(LZ) обозначают переход сигнала из состояния низкого (высокого) уровня в состояние высокого (низкого) уровня, из высокоомного состояния в состояние высокого (низкого) Уровня и из состояния высокого (низкого) уровня в высокоомиое состояние соответственно 2. Косая линия между символами HL/LH, LH/HL, ZHjZL, HZ/LZ означает, что параметры имеют одинаковое значение для обоих переходов. 3 CSU (С2. LH-CI, LH) + tr (C2) + *f (C2) + tWH (C2)+SU (CI. LH-C2, HL) + *r (Cl)>0 <: 4. Поступление данных иа канал данных должно разрешаться сигналом RC. В этом случае ие происходит конфликтных ситуаций на канале данных и гарантируются временные соотношения, необходимые для правильного приема данных в микропроцессор. 5- *У (D-C2, LH) <iV(RC, HL-C2, LH) при ( С, HL-C2,LH) > 50 не; iy (D-C2. LH) = ° <: P V (RC, HL-C2, LH)< - *V(D-C2, LH)v (RC, HL-C2, LH) v (A-Tr, LH) *V (D -tr, LH) sU (Ci, LH-CI, LH) + +л (C2, + *SU {Tr, HL-D, LHIHL) c-sU (C2, LH-C\, LH)° v (D, A, HZILZ-TR, LH) hu (C2, LH- CI, LH)*r (C2) = = V (D, A, LZ/HZ-HLDA, LH) sU (C2, LH-CI. LH)+r (C2) *° - *SU (TR, HL-A,HL/LH)c~sU (C2, LH-Cl, LH)~r (C2) Основные параметры микросхемы в диапазоне температур от -10 до -t-TCC и напряжениях питания Ccci =5,0 В±5 %; Ucc2 - = 12,0 В±57о, и,о=-5,0 В±б% приведены в табл. 3,8. 3.2. Микросхема КР580ВВ51А Микросхема КР580ВБ51 А-универсальный оинхронно-асннхронный приемопередатчик (УСАПП), предназначен для аппаратной реализации последовательного протокола обмена между микропроцессором КР580ВМ80А {КМ1810ВМ86) или другим устройством, способным запрограммировать данную микросхему на требуемый режим работы, и каналами последовательной передачи дискретной информации. Микросхема УСАПП преобразует параллельный код, получаемый от центрального процессора, в последовательный поток символов со служебными битами н выдает этот поток в последовательный канал связи с различной скоростью, а также выполняет обратное преобразование; последовательный поток символов - в параллельное 8-разряд.ное слово. Передаваемая и принимаемая ин<юрмаиня при необходимости может контролироваться на четность (нечетность). Микросхема УСАПП программируется на выполееиие почти всех применяющихся в настоящее время протоколов последовательной передачи данных и работает в двух режимах: синхронном и асинхроииом. Программирование микросхемы иа тот нли другой режим работы выполняется записью в соответствующие регистры слов инструкции режима служебных снихрооимволов и инструкции комацды. Максимальная скорость передачи/приема информации по последовательному каналу 64К бод, минимальная ие ограничена и определяется внешними устройствами (ВУ). Условное графическое обозначение микросхемы приведено иа рнс, 3.5, Н1аэи>аченне выводов - в табл. 3.9, структурная схема показана на рис. 3.6. Основными управляющими сигналами являются: wr, rd, co/d. cs. Возможные варианты сочетания управляющих сигналов и направления передачи информации в системе приведены в табл. 3.10, Микросхема может работать в двух режимах. Синхронный режим характеризуется не- 17 J 18 IT тхс cts bsr с cj rd со/в В7 В6 В5 Bi ВЗ Ш В! ВО txenh TxRBY rxrby synbet/bb Рис. 3.5. Условное графическое обозначение КР580ВВ51А syhmt/bv  Рнс. 3.6. Структурная схема КР580ВВ51А Вывод Обозначение /, 2, 5-5, 27, 28 13 14 15 16 18 19 20 21 22 23 24 ~CS COlW RxRDY TxRDY SYNDET/BD 25 26 d2-d7, do, Dl RxD GND TxEND TxD С SR DSR* RTS* DTR* Гип вывода Функциональное назначение выводов Входы/вы ХОДЫ Вход Вход Вход Вход Вход Вход Выход Выход Вход/выход Вход Выход Выход Вход Вход Вход Выход Выход Вход * Сигналы общего назначения, других целей Канал данных - обмен информацией между микропроцессором н микросхемой Приемник микросхемы Общий Синхронизация передачи Запись информации Выбор микросхемы Управление/данные Чтение информации Готовность приемника Готовность передатчика Двунаправленный трех-стабнльный программируемый вход/выход Готовность внещнего устройства принять данные Конец передачи Передатчик микросхемы Синхронизация Установка исходного состояния Готовность внешнего устройства передать данные Запрос приемника внешнего устройства на прием данных Запрос передатчика внешнего устройства на передачу данных Синхронизация приема Напряжение питания +5 В ±5% могут использоваться и для Таблица 3.10

Числа синхрасим- ВолоВ l-oauM сикхро- символ а- два синхро- симВала Вид синхронизации I-Внешняя О-Внутренняя Контроль 1-есть контроль а-нет контроля 1- четность О-нечетность Синхрон - ный решим

jr7\i)s\i>s\i><f\ja\i>?\B/\j>o

Контроль hecTb контроль О-нет контре ля 1-четность О-нечетность

Рис 3 7 Форматы инструкции режима для синхронного (а) и асинхронного (б) видов работы прерывным потоком пеедаваемой/приннмаемой информации. Для устаиовлення синхронизации между передатчиком/приемником микросхемы КР580ВВ51А и приемником/передатчиком внешнего устройства и выделения из последовательного потока символов полезной нн-формацнн в поток информации вводятся кодирующие слова (оинхросимволы). Информационная (б-8 бит) и временная длины снн-хросимвола н слова данных рамы. Если между словами данных имеются временные промежутки, то они заполняются син-хросимволамн. Синхросимволов может быть один нлн два (устанавливается программно) Если запрограммирован контроль данных по четности (нечетности), то после каждого слова данных вставляется бит контроля Сигналы иа внешних входах микросхемы асинхронны по отношению к онгналу С. Однако соотношение частот общей синхронизации микросхемы (/с) н частот сиихронизацин передачн/прнема быть должно fj<fc/30, / -<fc/30. При этом обеспечивается скорость передачи/приема информации v = Tx{Rx) =0-т-64 К бод. Скорость численно равна частоте оннхроннзацнн пере-дачн11приема и определяется в указанном выше диапазоне возможностями внешнего устройства. Асинхронный режим характеризуется одиночными посылками информации, инициализация которых определяется либо микропроцессором системы (где стоит микросхема КР580ВВ51А), либо внешним устройством В начале каждой посылки устанавливается отрицательний импульс старт-бит , длительность которого равна биту данных Старт-бит* служит для ввода в синхронизацию пе- редатчика/приемника микросхемы КР5вОВВ51А н приемника/передатчика внешнего устройства В конце каждой посылки устанавливается по ложительный импульс стоп-бит , длительность которого может равняться 1, 1,5 и 2 длительностям бита информации (устанавливается программно); стоп-бит служит для определения конца посылки Асинхронный режим имеет три подрежима, отличающихся друг от друга различым соот-ношеннем численных значений частот сннхро-низацни передачи/приема к скорости передачи. подрежим 1:1 соотношения частот общей оннхроннзацнн микросхемы и синхронизации передачи/приема, а также скорость передачи аналогичны синхронному режиму, подрежим 1:16- ТхС 16 = 0-19,2 К бод; RxC 16 подрежим 1:64: Тх = = 0-19,2 К бод; =0-9,6 к бод; Уп, = - = 0-9,6Кбод В подрежимах 1:16 и 1 64 должны выполняться условия: f,</с/4.5; f-<fc/4,5

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||