| |

|

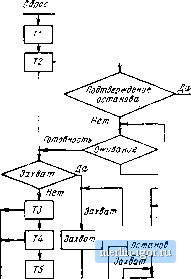

Строительный блокнот Корпуса микропроцессорных микросхем 2 Цикл чтения ЗУ - чтение ЗУ по содержимому программного счетчика или содержимому одного из регистров ВС, DE, HL. 3 Цикл записи в ЗУ - запись в ЗУ по содержимому одного из регистров ВС, DE, HL 4. Цикл тения стека - чтение ЗУ по содержимому указателя стека. 5 Цикл записи в стек - запись в ЗУ по содержимому указателя стека 6 Цикл ввода - ввод информации в регистр peiy.TbTara (аккумулятор) ш внешнего . угтронства 7. Цик.1 вывода--вывод информации из регистра результата во внеишее устройство. Лтовность останова Готовность V Подтдермдение останова  Готовность  вахвап }опрос прёрьтнйя Захват - Захват Запрос прерывал 1я Разрешение прерывания Захват Захват Захват Захват Установка триггера запроса прерывания CSpoc Подтввршдение останова Рис. 3.4. Диаграмма состояний типичного машинного цикла КР58ПВМ80А 8. Цикл прерывания - прием кода команды RST или CALL из контроллера прерываний. 9. Цикл останова. 10. Цикл прерывания при останове - прием кода команды RST или CALL при выводе микропроцессора из режима Останов по прерыванию. Наименования сигналов состояния, соответствие их разрядам канала данных, а также типам машинных циклов приведены в табл. 3.4. При выполнении команд микропроцессор может переходить в одно из трех состояний: ожидание , захват и останов , длительность которых определяется внешними управляющими сигналами. Сигнал высокого уровня на входе RDY обеспечивает автоматическое выполнение команд программы микропроцессором с частотой тактовых сигналов. Если на выводе RDV установлен сигнал низкого уровня, то микропроцессор переходит в режим Ожидание и формирует выходной сигнал WI высокого уровня. Сигнал RDY может быть использован для согласования работы микропроцессора с работой медленнодействующих устройств, если длительность их цикла обращения составляет более одного периода тактовой частоты, а также для организации пошагового (по циклам) выполнения команды или покомандного выполнения программы. При подаче на вход HLD сигнала высокого уровня микропроцессор переходит в состояние захват и подтверждает переход в это состояние формированием сигнала высокого уровня на выходе HLDA. Буферные схемы канала адреса и данных микропроцессора переключаются в высокоом-ное состояние, а выходные управляющие сигналы в состояние низкого уровня (за исключением сигналов TR и HLDA). Микропроцессор переходит в состояние Захват в такте ГЗ, если выполняется цикл чтения и на входе RDY сигнал высокого уровня, и в такте, следующим за ГЗ, если выполняется цикл записи. Сигналы HLD и HLDA ПОЗВОЛЯЮТ организовать режим прямого доступа к памяти для любого внешнего устройства, формирующего сигнала HLD. При выполнении команды HLT микропроцессор переходит в состояние останов и переводит буферные схемы канала адреса и данных м высокоомное состояние. Из состояния останов микропроцессор выходит прн наличии сигнала высокого уровня на одном из его входов: на входе S/?--микропроцессор начинает работать с такта 7 1 цикла Ml, на входе HLD - микропроцессор переходит в состояние захват , а после перехода сигнала HLD на низкий уровень возвращается в состояние останов , на входе INT - микропроцессор переходит к выполнению цикла прерывания при останове с такта Г/, если команде HLT предшествовала команда El разрешение прерывания , иначе остается в состоянии останов .

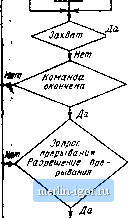

Сигнал высокого уровня на выводе INT позволяет прерывать выполнение текущей программы и переводить микропроцессор на выполнение подпрограммы обслуживания устройства, выдавшего запрос прерывания При поступлении сигнала INT микропроцессор (после окончания текущей команды) переходит с такта Т1 к выполнению машинного цикла Прерывание в том случае, если прерывание было разрешено ранее командой EI При выполнении цикла Прерывание в такте TI микропроцессор выдает по шине данных сигнал состояния Под тверждение прерывания , который использу ется 1ля разрешения выдачи из внешнего конт роллера прерывания (КР580ВН59) на канал данных системы команды и адреса перехода на подпрограмму прерывания По окончании под программы прерывания осуществляют возврат к прерванной программе Сигнал высокою уровня на входе SR (дли тельность которого должна быть не менее трех периодов тактовой частоты) устанавливает микропроцессор в исходное состояние триггер разрешения прерывания, триггер захвата, ре гистр команд, регистр признаков и регистр ад реса команды устанавливаются в нулевое сое тоянне После окончания действия сигнала SR микропроцессор производит первое обращение за чтением комаиты к ячейке памяти по адресу 0000,6 Система команд микропроцессора состоит из 78 базовых команд, которые можно разде лить на пять групп команды передачи данных - используются для передачи данных из регистра в peincTp, из памяти в регистр и регистра в память, арифметические команды - используются для сложения, вычитания, инкремента или декремента содержимого регистров или ячейки памяти, логические команды И.ИЛИ, исключающее ИЛИ, сравнение, сдвиги, команды переходов- используются для ус ловных н безусловных переходов, вызова подпрограмм н возврата нз них комаиды управления, ввода/вывода и работы со стеком - используются для управления прерыванием, регистром признаков, ввода и вывода информации В микропроцессоре КР580ВМ80А принят формат информационного слова, представляющего собой 8 разрядное двоичное слово (байт) Формат информационного слова (данных) 1де D7 - старший разряд слова, DO-младший разряд Отрицательные числа хранятся в памяти в дополнительном коде Формат команды зависит от типа операции и может быть одно двух или трехбайтовым Байты двух и трехбайтовых команд должны храниться в ячейках памяти, следующих одна за ipyroH Атре( первого банта всегда является а ipe<4JM ко 1Я от рацин Формат команд микропроцессора: Адрес ячейки памяти Байт В1 Байт В2 Байт 81 Байт В2 Байт ВЗ Однобайтовая команда

Двухбайтовая команда

операции Данные или адрес операции Данные или адрес

* с end обозначает группу команд, tWZ, CZ. CNC, СС, СРО, СРЕ, CP, СМ ** end обозначает группу команд iA-Z, RZ, RNC RC, RPO, НРЕ, RM

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||