| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Адрес Микропрограммная память ПоЛГ мси Т Условия Пале сам команда На Vommmi Т Т Т Т ~ЛанныеТаш~пШпсремР\ TcO-iaxm-HA3\cO,-cm\SR\LS8\№\zn\SL \COO-m\C05-COI2\CW3\m I каза- .....- I - j- i --I шель 1С NA Ш 0 CO 18 0 , К1800ВУ1 f Шина OS m sm Устройство синхронизации (К1800ВБ2) KI800BT3 СЯО A SYH BB P ZD CO(ALU) COIBSF) CBlW Шина IB Шина OB IS CRT OS 2JJ KWOOSTd COIALU) COiBBF] A SYHUB Шина A Шина D В Рис. 10.31. Структурная схема быстродействующего процессора, реализованного на микросхемах серий К1800 и К500 Структурная схема быстродействующего процессора, реализованного на МПК серии К1800, приведена на рис. 10.31 . Система команд процессора выбирается разработчиком применительно к устройству, в котором процессор будет использован. В качестве памяти должна использоваться память ППЗУ, реализованная на К500РЕ149. Для выполнения арифметико-логических операций в процессоре применена микросхема К1800ВТЗ, имеющая блок регистров. Две микросхемы К1800ВТЗ управляют также 1б-разрядными щниами ввода и вывода данных. Одна микросхема К1800ВУ1 осуществляет микропрограммное управление и адресацию. Программа процессора хранится в микропрограммной памяти. Синхронизацию, запуск и профилактику процессора обеспечивает микросхема К1800ВБ2. Для реализации условных переходов используются несколько микросхем серии К500. Таким образом, на одной печатной плате можно разместить весь процессор. Сигнал синхронизации микросхемы К1800ВУ1 выдает на адресную шину начальный адрес управляющей памяти. Затем из микропрограммной памяти на входы микросхемы К1800ВТЗ передаются коды для считывания и обработки данных и вывода результата или его записи в память. Одновременно с работой ALU нз памяти микропрограммы и блока условных переходов выдается новый адрес на входы К1800ВУ1. .Микропрограммирование позволяет с помощью такого процессора выполнять различ- ные операции (табл. 10.57). Пять программ: сложение, вычитание, исключающее ИЛИ, умножение и деление - это только часть программ такого процессора. При необходимости можно увеличить аппаратную часть процессора. Процессор работает с входными данными в виде одного 16-разрядного слова илн двух слов параллельно по восемь разрядов каждый. Ответ выдается в виде 16-разрядиого слова или двух 8-разрядных слов параллельно. Два 8-разрядных операнда считывают программы операций сложения, вычитания и исключающее Таблица 10.57

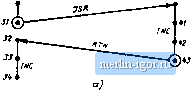

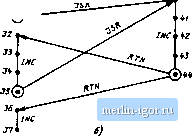

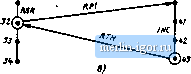

или и выдают ответ в виде 8-разрядиого слова. Остальные младшие разряды устанавливаются в 0. Программа умножения считывает 8-разрядиые множимое и множитель и выдаег 16-разрядный ответ. Программа деления сначала считывает 16-разрядное делимое, затем 8-разрядный делитель. Результатом деления является 8-разрядное частное и 8-разрядный остаток. Программа выполнения операции в процессоре представлена в табл. 10.58. Рассмотрим пример выполнения неповторяющейся подпрограммы (рнс. 10.32, а). Для реализации данной подпрограммы используются трн команды: JSR, INC и RTN. При адресе слова 30 адрес 31 заносится в RGO, к настоящему адресу (31) прибавляется 1 и он пересылается в RGS. Подпрограмма начинается с адреса 40 и заканчивается адресом 43. Затем по команде RTN содержимое RGS пересылается в RGO и продолжается выполнение основной программы, начиная с адреса 32. На рнс. 10.32,6 приведен пример повторяющейся подпрограммы, выполняемой по команде RSR, которая загружает регистр RG1 числом повторений {FF), являющимся дополнением до 2 требуемого числа. Выход О триггера Основная праерамма 30 Подпроерамма  Основная программа 1У Оадпрограмма *в  Основная команда 31 Повторяющаясякотнва  Рис. 10.32. Схема выполнения неповторяющейся подпрограммы (а), повторяющейся подпро граммы (б) и повторяющейся команды (в) I АОЗ I А02 I А01 \ А02 \ CK-LBS Входы ALU CB-MBS \ l!3\ R2 \ В1\ ВО \ Выховы ALU Рис. 10.33. Передача информации в АЛУ микросхемы К1800ВТЗ прн сдвиге влево RSQ блока управления шинами устанавливается в 1. Подпрограмма начинается с выполнения команды JSR (переход к подпрограмме). Адрес подпрограммы 40 передается в RGO, сумма настоящего адреса 31 и переноса передается в RG4. В конце каждого цикла подпрограммы (адрес 44) выполняется команда RTN и содержимое RG4 передается в RGO (адрес 32), и если прн этом /?5Q=1 и RGl=!i=FF, то содержимое RG1 увеличивается на 1. Если же RGl = FF, то RSQ устанавливается в О и RTN переходит к выполнению основной программы по адресу 36, а содержимое RG1 приравнивается FF. В повторяющейся команде (рнс. 10.32, в), как и в повторяющейся подпрограмме, выполняется команда RSR, в RG] загружается, код 11111100, RSQ устанавливается в 1 и число циклов команды равным 4. Затем выполняется команда RPI. При выполнении первых трех циклов повторения содержимое RG1 увеличивается иа 1. В течение последнего цикла триггер RSQ устанавливается в О и RGO переходит в следующий адрес 32, который продолжает программу. Прн 8-разрядном адресе слова максимальное число повторений подпрограмм и команд равно 256. Программирование выполнения арифметических и логических операций, а также выполнение сдвига рассмотрим иа примере программирования работы микросхемы К1800ВТЗ. Операции сложения и вычитания {ADD, SUB) выполняются следующим образом: АDD : (ЛО) -f (SO)-P--CR-LBS; SUB I {AO) + {BO)-P-\-CR-LBS. При операции сдвига влево {ASL, LSL) происходит сложение выбранного операнда с самим собой. Для ASL (COS = 0) признак переполнения вырабатывается прн изменении состояния в знаковом разряде (рис. 10.33). Как при сложении, так и при вычитании, ускоренный перенос минимизирует время задержки распространения сигнала. При арифметическом сдвиге вправо (ASR) во всех К1800ВТЗ, кроме микрос1хемы, содержащей самый старший разряд, производится логический сдвиг (COS = 0). В микросхеме, содержащей самый старший разряд, сигнал С08 должен быть равен нулю. Прн этом знаковый разряд сохраняет свое значение и передается на выход CRO и на следующий разряд вправо. При использовании схемы ускоренного переноса, для выполнения операции ASR, LSR (рис. 10.34) ее работа блокируется. На выво--де CRP-ZD вырабатывается признак нуля, а

Примечание. - - нет операции, состояние не изменяется.

|