| |

|

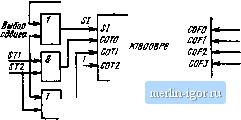

Строительный блокнот Корпуса микропроцессорных микросхем при распространеини знака в многоразрядном сдвигателе для арифметического сдвига вправо. Микросхема многоразрядного программируемого сдвигателя К1800ВР8 позволяет реализовать различные по структуре и быстродействию устройства сдвига информации. На рис. 10.26 приведена структурная схема 16-разрядного сдвигателя. Для выполиення операций сдвига необходимо дополнительно к микросхеме К1800ВР8- добавить три двух-входовых логических элемента (два ИЛИ и одни И) для управлеиия видом сдвига и знаком. Структурная схема 32-разрядиого сдвигателя показана на рис. 10.27. Схема состоит из четырех микросхем К1800ВР8 и девяти дополнительных логических элементов серии К500. Время выполнения сдвига в таком сдвигателе определяется временем задержки одной микросхемы К1800ВР8. Управление выбором сдвига осуществляется дешифрирующей схемой, реализованной на микросхемах серии К500 и формирующей управляющие сигналы. Для построения схем сдвигателей на число разрядов более 16 можно выбирать одно из двух возможных технических рещений. Если операции сдвига необходимо выполнить за более короткое время, то число микросхем К1800ВР8 и дополнительных микросхем серии ins vm moi то i-1 i  ггтт - ms wr soqi boo Рис. 10.26. Пример подключения микросхем К1800ВР8 в 16-разрядном программируемом сдвигателе К500 возрастает. Сравнение двух 64-разрядных сдвигателей, выполняющих операцию сдвига с временем задержки одной микросхемы KI800BP8 и временем задержки двух микросхем, показывает, что в первом случае сдвигатель содержит 16 микросхем К1800ВР8 и 26 микросхем серии К500, а для схемы второ го сдвигателя необходимо иметь 10 микросхем К1800ВР8 и 3 микросхемы серии К500. В табл. 10.53 приведены основные параметры К1800ВР8 прн температуре окружающей среды 25 °С. COFU mooBPS ЛП5-Л10 uw-mo si сото COFO COTl COFI COTZ COfZ mis-soo corj KieooBPe sns-m ST COTO COFO COT! COP! MCOTZ COFZ vas-Boo coFj BOji-Bois cofz COP! COFO K!800BPS *SI BIIS-BIO .* COFO COTO 1 J COFI COTl -* COFZ COTZ COFJ MS-BOO KI800BP8 SI В115-Ш0 COFO COTO COF! COTl COFZ COTZ COFJ ms-voo Рис. 10.27. Структурная схема 32-разрядного программируемого сдвигателя на четырех микросхемах К1800ВР8 и микросхемах серии К500

10.9. Микросхема К1800РП16 Микросхема К1800РП16 - буферная память (RAM), предназначена - для выполнения функции блока регистров в процессоре, а также буферного интерфейса памяти для периферийных устройств. Емкость матрицы регистров составляет 32X2 слова по 9 бит. Емкость памяти может быть увеличена наращиванием. Условное графическое обозначение микросхемы приведено на рис. 10.28, назначение выводов - в табл. 10.54, структурная схема показана на рис. 10.29. Микросхема RAM состоит из двух оСдина-ковых частей, каждая из которых включает усилители и формирователи записи данных AD и BD, дешифраторы адресов АА и ВА, блоки контроля четности адресов АА и ВА ч данных, усилители считывания даииых AD и BD регистры данных AD и BD, матрицы памяти Л и S и триггеры ошибки. Шины данных - 9-разрядные двунаправленные, шииы адресов АА и ВА - входные 5-разрядные. Каждая часть имеет входы разрешения записи с шии данных в память и входы разрешения выдачи данных из памяти на выходные шины. Синхронизация работы обеих частей микросхемы осуществляется синхросигналами SYNA и SYNB. Вход управления SR общий и устанавливает в исходное состояние триггеры ошибки и регистры данных. Микросхема К1800РП16 является модификацией К1800РП6, поэтому принципы работы отдельных блоков микросхем аналогичны (см. § 10.6). В микросхеме К1800РП16 исключена возможность автоматической перезаписи данных из одной части матрицы в другую, что позволило в 2 раза увеличить емкость матрицы памяти (с 32 до 64 слов) по сравнению с К1800РП6. В табл. 10.55 приведены основные эксплуатационные параметры К1800РП16 при температуре окружающей среды 25 °С. Вывод 2-6. 8-11 7, 17 12, 36 13-16, 18-22 23 26 27 28 29-34 35, 37-41 42 43 44 45 47 48 Обозначение bd1, bd2, bdo bd7, bd8, bd6-bd3 Тип вывода Функциональное назначение выводов ad3-ad6. ad8, ad7, ADO, AD2, ADl syna ead ewa aao, aa1-aa5 ba5-ba1, bao Jynb Ir erb co Входы/ выходы Входы/ выходы Выход Вход Вход Вход Входы Входы Вход Вход Вход Вход Выход Вход Напряжение -5,2 В питания Двунаправленные выводы шины данных bd, разряды 0-8 Общий выходных транзисторов Общий схемы Двунаправленные выводы шины данных ad, разряды 0-8 Ошибка четности данных нлн адреса АА Синхронизация выходного регистра АА Разрешение выдачи данных на шину ad Разрешение записи из шины ad в память Адреса АА - разрядов О (на четность), 1 (младшего) - 5 (старшего) Адреса ВА - разрядов О (иа четность), 1 (младшего) - 5 (старшего) Разрещение записи из щины bd в память Разрешение выдачи данных на шину bd Синхронизация выходного регистра ВА Установка в исходное состояние триггеров ошибки и выходных регистров Ошибка четности или адреса ВА данных Управление режимом установки Е. л. 38 37 АА RAM О 1 2 3 4 5 2 3 5 6 7 8 IL J4. Ж Ж Ж Ж 2 3 4 S 6 7 4 2. ERByJH Рис. 10.28. Условное графическое обозначение К1800РП16

|