| |

|

Строительный блокнот Корпуса микропроцессорных микросхем SYN. Синхрона затор пуска Формиро-- батель 1литель-ности синхро -сигналаб COS 1 блок управления рети мом ра - доты mpMJf полного цикла ~~Г~ СЗдига-тепь me/tt шт фал Вь/хоб-нь/е усилители Формира/а-ше/гь длигпейь -пасти после-бнегя синхрс имо!/л)са Вход управления наращиванием С06, вы-~сса признака последней фазы синхросигналов LPO и вход разрещения выработки синхросигналов LPI используются при объединении двух или более микросхем. Режим работы управляется сигналами СОЮ (однократный - тактовый), СОЯ (работа - профилактика), С08 (запуск - остановка), различные комби-*-С07 нации которых приведены в табл. 10.26. .Микросхема имеет контрольный выход состояния ССО. Сигнал ССО = П при поступле- ~ср; CP2 -CPS ~CF!, w штро-гсследнего cuHxpocuiHO/a Таблица 10.26 Рис. 10.8. Структурная схема К18()0ВБ2 ную работу микросхем МПК К1800 в устройствах цифровой автоматики и вычислительной техники. Число выходных фаз, длительность синлросигиалон каждой фазы, запоминание синхросигнала и другие режимы работы FT программируются с помощью внешних сигналов, поступающих на соответствующие входы. .Микросхема может быть также использована ;ля выработки синхросигналов н устройствах, построенных на базе микросхем серии К500. Условное графггческое обозначение микросхемы приведено на рис. 10.7, назначение вы водов - в табл. 10.25, структурная схема tto-казана на рис 10.8. Микросхема содержит: синхронизатор пуска, формирователь длительности синхросигналов, блок управления режимом работы, 6jtoK контроля полного цикла, сдвигатель, формиро ватель числа фаз, формирователь длительно сти последнего синхросигнала, блок контроля последнего синхросигнала и выходные усилители. Запуск микросхемы производится асинхрон ным сигналом произвольной длительности ни входе 57 . В результате вырабатываются синхросигналы СР1-СР4, длительность которых определяется тактовой частотой импульсов на входе SYN. Сброс всех выходов синхросигналов в О выполняется сигналами лог. О на входе SR. С помощью управляющих сигналов на входах СОО-СОЗ осуществляется программирование длительности синхросигналов CPI-СР4 соответственно, причем при СО, = 0 сигнал CP, имеет единичную длитель ность, при С0, = 1 CP, имеет двойную длительность. Управляющие входы С04, С05 позволяют программировать число фаз синхросигналов от одной до четырех. Управление длительностью последнего выходного синхросигнала в режимах однократная фаза и остановка на фазе производится сигналом на входе С07. При С07- 1 выходные синхросигналы имеют двойную длительность в зависимости от состояния управляющих сигналов на входах СОО-СОЗ. При СО7 = 0 в указанных режимах происхо-.шт хранение последнего синхросигнала в со стоянии лог. 1. Режим работы Операция Управление Профи-лакти-чес-кий Запуск Остановка в конце цикла Остановка на фазе Остановка Единичный цикл Единичная фаза Рабочий Запуск Остановка в конце цикла Остановка иа фазе Остановка Единичный цикл Единичная фаза Таблица 10.27

Таблица 10.28

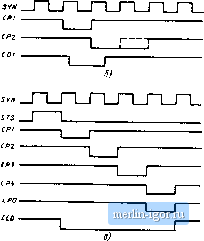

SYM . *Г5 .  Рис. 10.9. Временные диаграммы. и формирование синхросигнала iijcKa STS; б формирование второй фаш синхросигнала двойной длительности; в единичный цикл v*JтлJlJlJглJlJlJlJlJmл. атз CPI-СР2- гп СРЗ- iv JmлJlJmRгшJlJтлJг сов CPI-СР2-СРЗ-СРк- -1 г 1 Г 1 Г 1 Г 1 Г L r jmjinnjTnjmrLTL 1 Г~1 п -и-и- -и-и- ССО I S\nJU\I\I\I\Pd\IU\- se П l I I CP, -ы-u- cp2-u-u- CPS -L I Рис. 10.11. Временные Д11аграммы работы микросхемы в рабочем режиме: а единичная фа1а; 6 остановка на фан-. CP:i двойной длительности НИИ сигнала SR, либо при окончании onepauHi единичный цикл либо при остановке в кон це цикла, ССО- 1 в остальных случаях. Внешние сигналы произвольной длительно сти 57 в синхронизаторе пуска преобразуются во внутренние синхронные сигналы SYN, дли тельность которых равна длительности перио .la синхросигналов (рис. 10.9, а). Формирова тель числа фаз вырабатывает выходные им пульсы-фазы, число которых зависит от состоя ния управляющих сигналов на входах С04 i С05 (табл. 10.27). Формирователь длительности фаз синхросигналов позволяет увеличить с помощью уп равляющих сигналов на входах СОО-СОЗ длительность некоторых или всех выходных синхросигналов CPI-СР4 в 2 раза. Длительность синхросигналов в единичном режиме равна длительности периода тактирующих сигналов SYN. Программирование длительности фаз синхросигналов производится согласно табл. 10.28. Сдвигатель обеспечивает определенную последовательность всех синхросигналов. Все четыре фазы появляются или отсутствуют на Рис 10.10. Временные диаграммы работы микросхемы в профилактическом режиме: а единичный цикл, четыре фазы. CPI и СР4 двой ной длительности; б - остановка в конце цикла, че тыре фaы входах в строго определенные моменты времени с соблюдением последовательности 1-2-3-4. Формирователь длительности последнего синхросигнала задает длительность последнего выходного синхросигнала в режимах единичная фаза и остановка на фазе . Режим работы блока управляется сигналом на входе С07. Временные диаграммы работы микросхемы приведены на рис. 10.9-10.11. На рис. 10.10 временные диаграммы приведены для работы микросхемы в профилактическом режиме, ни рис. 10.11 -в рабочем режиме. При многофазной системе синхронизации выработку синхросигналов в процессоре обеспечивают объединением нескольких микросхем К1800ВБ2. На рис. 10.12 показано соединение двух микросхем, которые могут вырабатывать до восьми синхросигналов. При объединении нескольких микросхем К1800ВБ2 одна {А) является основной, а все остальные (В) подчиненными. Если работает одна микросхема, го она является основной. На вход С06 осиов- /(1800862 В cm COS COS К1800ВБ2 A ттпи csicascof Рис. 10.12. Пример объединения двух микросхем К1800ВБ2, в устройстве синхронизации Таблица 10.29

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||