| |

|

Строительный блокнот Корпуса микропроцессорных микросхем Таблица 10.12

Таблица 10.13

Кроме указанных пересылок, возможна пересылка информации из накопителя и на вход сдвигателя прн СО7=0. Сдвигатель, расположенный в микросхеме после сумматора, позволяет выполнять сдвиг влево, логический и арифметический сдвиг вправо и сквозную передачу данных с помощью управляющих сигналов C0I3 и €014 (табл. 10.12). Информация на сдэигатель поступает от накопителя прн СО7=0 и от сумматора при С07=1. Использование выводов LBS и MBS прн выполнении операции сдвига приведено в табл. 10.13. Работа фиксатора и накопителя синхронизируется входами SYN2 и SYNI соответственно. Информация с шииы ОВ заносится на D-триггеры фиксатора при SYN2=0. Синхронизация D-триггеров накопителя осуществляется положительным фронтом синхросигнала SYN], и тогда информация со всех вдодбв накопителя передается на его выходы. Мнкросхема выполняет 28 логических операций, 23 операции двоичной арифметики, 17 операций двоично-десятичной арифметики, арифметический и логический сдвиги. В логическом режиме работы микросхемы источником данных для сумматора могут быть D-трнггеры фиксатора шины ОВ, MUXO и АСС. Мнкросхема может выполнять полный набор логических операций, приведенных в табл. 10.14. В логическом режиме работы (СО/2=0) сумматор осуществляет исключающее ИЛИ над данными на входах ОХ и 0Y. Формирователь кодов при СО! 1=1 выполняет функции инвертора по состоянию на входе СОЮ. Источник информации для входов ОХ выбирается с помощью сигналов С02 и СОЗ, для входов ОК -с помощью сигналов СОО и С01 = С04=\ и объединяется по ИЛИ с со- держимым накопителя. Возможны и другие комбинации управляющих сигналов, дающие множество дополнительных операций и определяемые нз предыдущих таблиц истинности. В арифметическом режиме формирователь кодов и сумматор настроены иа арифметический режим работы с помощью С012-1, а С04 используется для приращения или вычитания 2. Сигнал на входе СОП выбирает двоичный или двоично-десятичный режим работы. Операнды, поступающие иа входы сумматора внутри микросхемы, определяются видом выполняемой операции. Большинство двоичных функций имеют двоично-десятичный эквивалент. В табл. 10.15 показаны арифметические операции, выполняемые в зависимости от управляющих сигналов. Как и для логических операций, другие комбинации управляющих сигналов и функций возможны и могут (в случае необходимости) устанавливаться с помощью предыдущих таблиц истинности. Таблица 10.14

Примечание. V - логическое сложение; - логическое умножение; № - сложение по модулю 2.

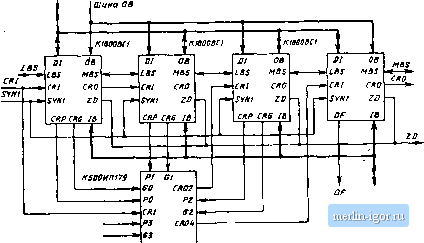

Примечание X - состояние не определено в двоично-десятичной арифметике, доп 9 полвеине до 9 шииы Dl Dl - до- В микросхеме К1800ВС1 могут пересылаться данные в накопитель и из него, в сдвнга-тель и из него. Пересылки определяются управляющими сигналами С05-С09 н С015 (табл. 10.16), Шина 01 Параллельное объединение микросхем К1800ВС1 позволяет строить АЛУ любой разрядности, кратной четырем. На рис. 10.3 приведена структурная схема 16-разрядного АЛУ, построенного из четырех микросхем К1800ВС1 ктовс!  Рис. 10,3. Структурная схема 16-разрядного АЛУ, реализованного К1800ВС1 и К500ИП179

и одной микросхемы ускоренного переноса К500ИП179. Управляющие входы СО0-СО15. SYN1 и SYN2 объединяются параллельно для всех четырех микросхем, а щины 01, ОВ и IB распределены по соответствующим щинам микросхем. Схема ускоренного переноса использует вход CRI в младщей схеме и выходы CRP, CRG трех младщих схем и образует выходной перенос для двух старших схем. Входной перенос CRI в младшей схеме определяется предыдущей логикой, входным переносом второй схемы является выходной перенос CRO младшей схемы. Выходным переносом всего блока АЛУ является выходной перенос CRO со старшей схемы. MBS каждой младшей схемы соединен со входом LBS следующей. Во время всех операций сдвига сигналы MBS старшей схемы выдают также состояние двигателя. Сигналы ZD микросхемы с помощью операции И формируют нули в АЛУ. Переполнение старшей схемы является переполнением АЛУ. Все выходы состояния АЛУ могут быть использованы прн выполнении микрокоманды Таблица 10.17

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||