| |

|

Строительный блокнот Корпуса микропроцессорных микросхем 9.6. Микросхемы К589АП16 и К589АГ12Ф Микросхемы К589АП16 - шинный формирователь (ШФ) и К589АП26 - шинный формирователь с инверсией (ШФИ), являются параллельными двунаправленными формирователями сигналов для управления магистралями (шинами) в цифровых вычислительных устрой- !L ] L. 5 т 1-1 ж - тг шз ого - П!3 SB0-DB3 1 ] Ж. 1L. 1 з в ТЮЕ CS mi mi W3< Рис. 9.22. Условное графическое обозначение К589АП16 Рис. 9.23, Условное графическое обозначение К589АП26 1 J UBt -FIM ли LI 2752 m шз Рис. 9.24. Структурная схема К589АП16 Рис. 9.25. Структурная схема К589АП26 cs,ncB 33BB-DB3 DOB-ЛОЗ Рис. 9.26. Временийя диаграмма работы К589АП16 й К589АП26

Примечание Выводы 2, 3, 5, 6, 10, II, 13, 14 имеют три состояния Таблица 9.25

ствах и представляют собой 4-каиал ьиые коммутаторы, имеюшие в каждом канале одну шину только для приема информации, одну шииу только для выдачи информации и одну двунаправленную шину для приема и выдачи информации. В ШФ информация проходит без изменений, в ШФИ - с инверсией. Условное графическое обозначение микросхем приведено иа рис. 9.22 и 9,23, назначение выводов - в табл. 9.24, структурные схемы показаны иа рис. 9.24 и 9,25, временные диаграммы работы - иа рис. 9.26. Для управления режимом работы и направлением выдачи информации служит схема, выполненная иа двухвходовых логических элементах И, Формирователи обеспечивают передачу информации при наличии лог. О иа входе CS выборки кристалла. При наличии лог. 1 на входе CS формирователи находятся в выключенном состоянии и выходы имеют высокое сопротивление (3-е состояние). При наличии на входе CS лог. О управление выдачей информации по шинам DO и DB осушествля- Таблица 9.26 Продолжение табл. 9.26

Параметр Обозначение Значения параметров [макс, (мни.)] для выходов Вво- DB3 Выходные напряжения низкого уровня. В: для выходов ООО- D03 при /н = 15 мА для выходов ВВО- DB3 при /н = 50 мА Выходное напряжение высокого уровня, В: для выходов ООО-ВОЗ при /н =-1 мА для выходов DBO- DB3 при /н = -10 мА 0,5 0,7 (3,65) (2.4) Примечание. Типовые значения тока потребления 95 мА напряжения низкого уровня для выходов DO0-DO3 0,4 В, для выходов DB0--DB3 0,5 В. Таблица 9.27

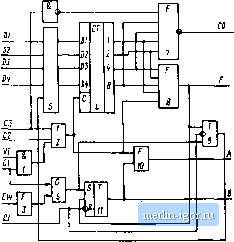

ется сигналом на входе управлеиия выдачей информации ОСЕ. Если на входе ОСЕ присутствует напряжение лог. О, то открыта передача информации с входов DI на выходы DB. При наличии на входе ОСЕ лог. 1 происходит передача информации с входов DB иа выходы DO (табл. 9 25). Статические и динамические параметры микросхем ШФ и ШФИ приведены в табл. 9.26 и 9.27 соответственно. 9.7. Микросхема К589ХЛ4 Микросхема К589ХЛ4 - многофункциональное синхронизирующее устройство (МСУ), предназначено для построения блоков радиоэлектронной аппаратуры с автономными синхронизаторами. Микросхема выполняет следующие операции: деление частоты с переменным коэффициентом деления; формирование импульсов дискретной линии задержки; формирование переменного пакета импульсов; формирование импульсов переменной длительности. Условное графическое обозначение микросхемы приведено на рнс. 9.27, назначение выводов - в табл. 9.28, структурная схема показана на рис. 9.28, временная диаграмма работы - на рис. 9.29. В состав микросхемы входят: / - входная логическая схема И; 2 - трехвходовая логическая схема ИЛИ; 3 -схема формирования импульсов стандартной длительности на импульсов начальной установки; 4 - 4-разрядиый двоичный счетчик; 5 - схема установки коэффициента перерасчета; 6 - генератор EW Ыш F2 Ш M CO F A Ж ± Рис. 9 27. Условное графическое обозначение К589ХЛ4

отиночных импульсов (ГОН); 7 - формирователь сигнала переноса; 8 - схема И делителя частоты; 9 - схема ИЛИ приема импульсов записи на схему установки в исходное состояние; 10 формирователь переменного пакета импульсов; )/ - формирователь длительности импульса. Микросхема К589ХЛ4 может работать в следующих режимах. Режим деления частоты. На вход 4 подается импульс произвольной длительности начальной установки с любого устройства, синхронизированного или не синхронизированного с импульсами тактовой частоты. Узел 3 формирует сигнал, который поступает на генератор одиночных импульсов 6 и подготавливает его для приема одного импульса тактовой ча-  стоты Fc, подаваемой на вход 3. С выхода узла 6 одиночный импульс поступает через Схему ИЛИ 9 иа вход узла установки в исходное состояние 5; прн этом счетчик 4 устанавливается в исходное состояние, которое определяется кодом иа входах 11-14. С входа 3 импульсы тактовой частоты подаются на один из входов схемы узла /, иа другой вход этого узла с входа 2 подается С1 . tp(ci-coi. А СЗ F С1 JP(CJ-C01 JP(CI-Bj r\ r\

tplci-e) Рис. 9.28. Стдуктурная схема К589ХЛ4 Рис. 9.29. Временная диаграмма работы К589ХЛ4

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||